- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- What is CONTROL SPSEL value?

What is CONTROL SPSEL value?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Freescale people,

I would like to know the implementation of SPSEL bit (bit[1]) value of CONTROL register of KInetis of which CPU is Cortex-M0+.

According to my experiment, SPSEL bit was fixed to 0 by KL25Z. This means the stack pointer would be always MSP even in the thread mode, doesn't it?

How about the other Kinetis MCUs?

Best regards,

Yasuhiko Koumoto.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Sorry for the delay reply.

I checked <ARM Cortex-m0+ generic user guide> with below description about CONTROL register :

In an OS environment, ARM recommends that threads running in Thread mode use the process stack and the kernel and exception handlers use the main stack.

By default, Thread mode uses the MSP. To switch the stack pointer used in Thread mode to the PSP, use the MSR instruction to set the active stack pointer bit to 1.

So I double check with KL25 MQX_LITE example and K60 MQX example, after the MQX RTOS boots up, it will switch the SP_process.

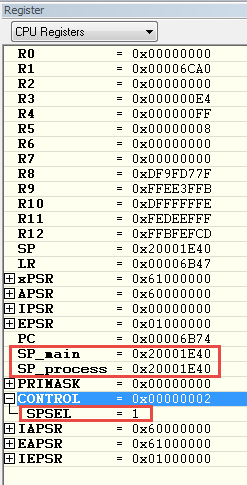

Below is KL25 MQX_Lite example CPU register info after MQX_Lite RTOS boot up:

And you could find below stack switch code at <boot.s> file, the SP_main and SP_process using the same SRAM address:

/* Prepare process stack pointer */

mrs r0, MSP

msr PSP, r0

/* Switch to proccess stack (PSP) */

mrs r0, CONTROL

movs r1, #0x2

orrs r0, r0, r1

msr CONTROL, r0

isb

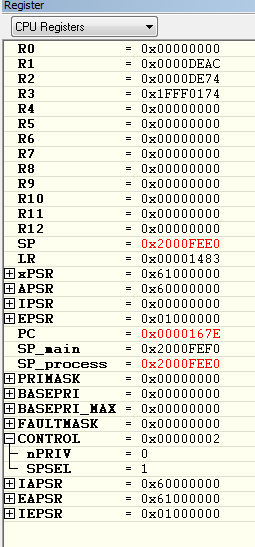

Below is TWR-K60D100M board running MQX example CPU registers status:

Here is the stack pointer switch code at <boot.s>

| /* Prepare process stack pointer */ | |

| mrs r0, MSP | |

| msr PSP, r0 |

| /* Switch to proccess stack (PSP) */ | |

| mrs r0, CONTROL | |

| orr r0, r0, #2 | |

| msr CONTROL, r0 | |

| isb #15 |

So, the CONTROL_SPSEL bit could be set at all Kinetis product.

The Stack Pointer (SP) is register R13. In Thread mode, bit[1] of the CONTROL register indicates the stack pointer to use:

• 0 = Main Stack Pointer (MSP). This is the reset value.

• 1 = Process Stack Pointer (PSP).

On reset, the processor loads the MSP with the value from address 0x00000000.

Wish it helps.

Have a great day,

best regards,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I agree with you, the Kinetis product is using SP_main as the current stack, which means the SPSEL bit in control register of ARM Cortex M4/M0+ core value is 0.

From the Kinetis reference manual with below description:

When the system exits reset, the processor sets up the stack, program counter (PC),and link register (LR). The processor reads the start SP (SP_main) from vector-table offset 0. The core reads the start PC from vector-table offset 4. (K70 RM)

This device supports booting from internal flash with the reset vectors located at addresses 0x0 (initial SP_main), 0x4 (initial PC), and RAM with relocating the exception vector table to RAM. (KL25 RM)

Wish it helps.

Have a great day,

best regards,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi again,

I reconfirmed the fact on my FRDM-KL25Z board. I have found SPSEL bit had been set to "1".

That is, we can modify CONTROL.SPSEL bit.

It is inconsistent with your comment. Did I misunderstand your comments?

Best regards,

Yasuhiko Koumoto.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Sorry for the delay reply.

I checked <ARM Cortex-m0+ generic user guide> with below description about CONTROL register :

In an OS environment, ARM recommends that threads running in Thread mode use the process stack and the kernel and exception handlers use the main stack.

By default, Thread mode uses the MSP. To switch the stack pointer used in Thread mode to the PSP, use the MSR instruction to set the active stack pointer bit to 1.

So I double check with KL25 MQX_LITE example and K60 MQX example, after the MQX RTOS boots up, it will switch the SP_process.

Below is KL25 MQX_Lite example CPU register info after MQX_Lite RTOS boot up:

And you could find below stack switch code at <boot.s> file, the SP_main and SP_process using the same SRAM address:

/* Prepare process stack pointer */

mrs r0, MSP

msr PSP, r0

/* Switch to proccess stack (PSP) */

mrs r0, CONTROL

movs r1, #0x2

orrs r0, r0, r1

msr CONTROL, r0

isb

Below is TWR-K60D100M board running MQX example CPU registers status:

Here is the stack pointer switch code at <boot.s>

| /* Prepare process stack pointer */ | |

| mrs r0, MSP | |

| msr PSP, r0 |

| /* Switch to proccess stack (PSP) */ | |

| mrs r0, CONTROL | |

| orr r0, r0, #2 | |

| msr CONTROL, r0 | |

| isb #15 |

So, the CONTROL_SPSEL bit could be set at all Kinetis product.

The Stack Pointer (SP) is register R13. In Thread mode, bit[1] of the CONTROL register indicates the stack pointer to use:

• 0 = Main Stack Pointer (MSP). This is the reset value.

• 1 = Process Stack Pointer (PSP).

On reset, the processor loads the MSP with the value from address 0x00000000.

Wish it helps.

Have a great day,

best regards,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hui_Ma,

thank you for confirmation. I understood well.

Best regards.

Yasuhiko Koumoto.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hui_Ma,

I confirmed your comment by both FRDM-KL25Z and FRDM-K20D50M.

We cannot make SPSEL bit of CONTROL register "1".

I wonder why such important information was not described in any Reference Manuals.

Best regards,

Yasuhiko Koumoto.