- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: UART Error on KL26Z128 using CodeWarrior

UART Error on KL26Z128 using CodeWarrior

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I'm having a issue when I try to read I2C with FXOS8700, and put it into board UART1, to visualize by Computer Serial Terminal. Is there any communication protocol to communicate between UART and OpenSDA? I attached code with the issue.

Thanks in advance,

Omar Valle Casas

Original Attachment has been moved to: inercial20.rar

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Update:

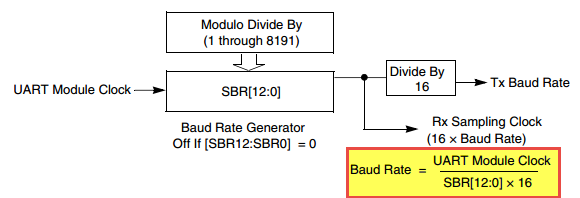

The UART Module Clock is the bus clock which does not seem to be configured. By default the Bus Clock is 20.97152 MHz, so:

SBR = 20.97152 MHz / (16 * 115200) = 11.3777

I suggest to change the bus clock to 48 MHz, it will produce a more accurate baud rate:

SBR = 48 MHz / (16 * 115200) = 26.0416

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Omar,

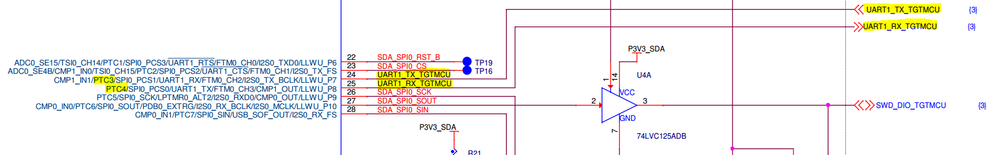

In the FRDM-KL26Z schematic (I suppose you are using a freedom board) you can see that the OpenSDA UART is routed to the PTC3 and PTC4 pins (UART1).

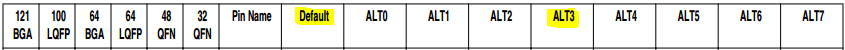

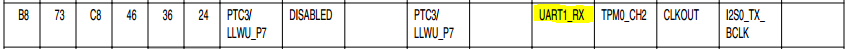

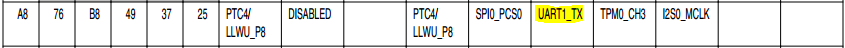

In the KL26P121M48SF4RM Reference Manual pinout you can see that the PTC3 and PTC4 pins are disabled by default. You need to select the alternative 3 in both cases in the PORTC_PCRx[MUX] register.

Best regards,

Earl Orlando.

/* If this post answers your question please click over the Correct Answer button. */

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I configured the SIM for Port enabling and didn't worked. I'm putting code inside message body to facilitate visualization.

void uart1_init (void){

/*habilitando o clock para a UART0 (pg.221)*/

SIM_SCGC4 = SIM_SCGC4_UART1_MASK;

SIM_SOPT5 |= SIM_SOPT5_UART1TXSRC(0);

PORTC_PCR3 = PORT_PCR_MUX(0x3); // Omar's 08_07_15

PORTC_PCR4 = PORT_PCR_MUX(0x3); // Omar's 08_07_15

UART1_BDH = 0x02;

UART1_BDL = 0x71; /* SBR = 26 */

// UART1_C4 = 0x03; /* OSR = 4 */ //Não existe

UART1_C2 |= UART0_C2_TE_MASK;

UART1_D = 2;

}

/*---------------------------------------------------------------------*/

/* ENVIA DADO PELA SERIAL */

/*---------------------------------------------------------------------*/

void uart1_send (int i2c1_data){

/*Se a flag de transmissao TDRE (pg.761) estiver igual a zero (buffer cheio), não deve fazer nada*/

while(!(UART1_S1&UART_S1_TDRE_MASK) && !(UART1_S1&UART_S1_TC_MASK));

UART1_D = i2c1_data;

}

/*---------------------------------------------------------------------*/

/* INICIALIZACAO DA I2C */

/*---------------------------------------------------------------------*/

void i2c_init(void){

/* O registrador System Clock Gating Control Register 4 (SIM_SCGC4) eh responsavel por habilitar o clock da I2C0 (pg.220) */

SIM_SCGC4 |= SIM_SCGC4_I2C0_MASK;

/* O registrador System Clock Gating Control Register 5 (SIM_SCGC5) eh responsavel por habilitar o clock da PORTE (pg.222)*/

SIM_SCGC5 |= SIM_SCGC5_PORTE_MASK|SIM_SCGC5_PORTC_MASK|SIM_SCGC5_PORTA_MASK;

/* O pino SCL do FSXO8700CQ está conectado ao PTE24 do KL26Z128 ---> CONFIGURACAO DE PTE24 = SCL : */

/* Pela tabela de Pinout (pq.176) , PTE24 = I2C0_SCL no modo ALT5 (0x5) */

PORTC_PCR24 |= PORT_PCR_MUX(0x5);

/* O pino SDA do FSXO8700CQ está conectado ao PTE25 do KL26Z128 ---> CONFIGURACAO DE PTE25 = SDA : */

/* Pela tabela de Pinout (pq.176) , PTE25 = I2C0_SDA no modo ALT5 (0x5) */

PORTC_PCR24 |= PORT_PCR_MUX(0x5);

/*O registrador Frequency Divider Register (I2C0_F) [I2C memory map, pg.722] recebe a frequência de operacao da I2C */

/*O I2C0_F deve receber o Clock Rate (ICR) [pg.723] . Neste caso : 0x14 ---> SDA hold time = 2.125us, SCL start hold time = 4.25us, SCL stop hold time = 5.125us */

I2C0_F |= I2C_F_ICR(0X14);

/* O registrador I2C Control Register 1 (I2C0_C1) [I2C memory map, pg.722] eh responsavel por habilitar a I2C0 */

/* Para habilitar , o bit IICEN (bit 7) [pg.724] deve ser setado (0x80) */

I2C0_C1 |= I2C_C1_IICEN_MASK;

/*------------------------------------------------------------------------------------------*/

/* CONFIGURACAO DE PTD0 PARA A INTERRUPCAO DE BORDA DE DESCIDA (INT1) DO FXOS8700CQ */

/*------------------------------------------------------------------------------------------*/

/* O registrador System Clock Gating Control Register 5 (SIM_SCGC5) eh responsavel por habilitar o clock da PORTD (pg.222)*/

SIM_SCGC5 |= SIM_SCGC5_PORTD_MASK;

/* O registrador Interrupt Status Flag Register (PORTx_ISFR) [pg.202] eh zerado, PTD0 é configurado como GPIO e como INT1*/

PORTD_PCR0 |= (0|PORT_PCR_ISF_MASK| // Limpa a flag

PORT_PCR_MUX(0x1)| // PTD4 eh configurado como GPIO [MUX, tabela pg.200]

PORT_PCR_IRQC(0xA)); // PTD4 eh configurado como interrupcao de borda de descida (0xA) [IRQC, tabela pg.200]

/*Habilitando a configuracao Nested Vectored Controller (NVIC) [pg.57] na porta D */

NVIC_ICPR |= 1 << ((INT_PORTC_PORTD - 16)%32);

NVIC_ISER |= 1 << ((INT_PORTC_PORTD - 16)%32);

}

/*---------------------------------------------------------------------*/

/* ESPERA I2C */

/*---------------------------------------------------------------------*/

void i2c_wait(void){

while(!(I2C0_S & I2C_S_TCF_MASK) );

}

/*---------------------------------------------------------------------*/

/* start I2C */

/*---------------------------------------------------------------------*/

void i2c_start(void){

i2c_wait();

I2C0_C1 = I2C_C1_TX_MASK;

}

/*---------------------------------------------------------------------*/

/* RESTART I2C */

/*---------------------------------------------------------------------*/

void i2c_restart(void){

i2c_wait();

I2C0_C1 = I2C_C1_RSTA_MASK;

}

/*---------------------------------------------------------------------*/

/* FECHA A TRANSMISSAO VIA I2C */

/*---------------------------------------------------------------------*/

void i2c_stop(void){

i2c_wait();

I2C0_FLT = I2C_FLT_SHEN_MASK;

}

/*---------------------------------------------------------------------*/

/* ESCREVE VIA I2C */

/*---------------------------------------------------------------------*/

void i2c_write(int data){

i2c_wait();

I2C0_D = data;

}

/*---------------------------------------------------------------------*/

/* LEITURA VIA I2C */

/*---------------------------------------------------------------------*/

int i2c_read(void){

int i2c_read_data;

i2c_wait();

I2C0_S = I2C_S_SRW_MASK;

i2c_wait();

i2c_read_data = I2C0_D;

return i2c_read_data;

}

/*---------------------------------------------------------------------*/

/* ENDEREÇAMENTO VIA I2C */

/*---------------------------------------------------------------------*/

void i2c_slaveREG_address(unsigned char addr){

i2c_wait();

I2C0_D = addr;

}

/*---------------------------------------------------------------------*/

/* INICIALIZACAO DO FXOS87OOCQ */

/*---------------------------------------------------------------------*/

void fxos8700cq_init (void) {

/* Setando FXOS8700CQ como slave

*

* Dos headers:

*

* DEFINIÇÃO DO ENDEREÇO DO FXOS8700CQ COMO ESCRAVO

* #define FXOS8700CQ_SLAVE_ADDR 0x1E --> SA0=0, SA1=0

*/

I2C0_A1 = FXOS8700CQ_SLAVE_ADDR;

/*CTRL_REG2 --> initiate a software reset;

*

* bits

* [0,1]: mods = 0b00 (normal) --> determines the Wake mode power and noise for acceleration measurements.

* [2] : slpe = 0 --> Auto-sleep is not enable.

* [3,4]: smods = 0b00 (normal) --> determines the Sleep mode power and noise for acceleration measurements.

* [5] : not used.

* [6] : rst = 1 --> Device reset enabled.

* [7] : st = 0 --> accelerometer self-test disabled.

*/

i2c_start();

i2c_slaveREG_address(CTRL_REG2); // COLOCA O ENDEREÇO DO REGISTRADOR DO FXOS NO BARRAMENTO DE DADOS

i2c_write(0X40); //ESCREVE NO REGISTRADOR

/*M_CTRL_REG1 --> Magnetic control register; set hybrid mode;

*

* bits

* [0,1] : m_hms = 0b11 --> Hybrid mode, both accelerometer and magnetometer sensors are active.

* [2,3,4]: m_os = 0b111 --> 4xOSR (for 400Hz).

* [5] : m_ost = 0 --> one-shot magnetic complete.

* [6] : m_rst = 1 --> one-shot magnetic reset is enabled, hardware cleared when complete.

* [7] : m_acal = 0 --> auto-calibration feature disabled.

*/

i2c_restart();

i2c_slaveREG_address(CTRL_REG1); // COLOCA O ENDEREÇO DO REGISTRADOR DO FXOS NO BARRAMENTO DE DADOS

i2c_write(0X5F); //ESCREVE NO REGISTRADOR

/*M_CTRL_REG2 --> Magnetic measurement features

*

* bit

* [0,1] : m_rst_cnt = 0b00 --> Automatic magnetic reset at the beginning of each ODR cycle (default).

* [2] : m_maxmin_rst = 0 --> Magnetic measurement min/max detection function reset:: No reset sequence is active.

* [3] : m_maxmin_dis_ths = 0 --> Magnetic measurement min/max detection function disable using the magnetic threshold event trigger: No impact to magnetic min/max detection function on a magnetic threshold event.

* [4] : m_maxmin_dis = 0 --> Magnetic min/max detection function is enabled (default).

* [5] : hyb_autoinc_mode = 1 --> hybrid mode enable.

* [6,7] : not used.

*/

i2c_restart();

i2c_slaveREG_address(M_CTRL_REG2); // COLOCA O ENDEREÇO DO REGISTRADOR DO FXOS NO BARRAMENTO DE DADOS

i2c_write(0X20); //ESCREVE NO REGISTRADOR

/*CTRL_REG1 --> initial data features

*

* bits

* [0] : active = 1 --> active mode.

* [1] : f_read = 0 --> fast-read mode disable, will work in normal mode.

* [2] : lnoise = 1 --> reduced noise mode.

* [3,4,5] : dr = 0b000 --> Output Data Rate (ODR) for hybrid mode (400 Hz).

* [6,7] : aslp_rate = 0b00 --> Configures the auto-wake sample frequency when the device is in Sleep mode (50 Hz).

*/

i2c_restart();

i2c_slaveREG_address(CTRL_REG1); // COLOCA O ENDEREÇO DO REGISTRADOR DO FXOS NO BARRAMENTO DE DADOS

i2c_write(0X05); //ESCREVE NO REGISTRADOR

/*XYZ_DATA_CFG -->The XYZ_DATA_CFG register is used to configure the desired acceleration full-scale range, and also to select whether the output data is passed through the high-pass filter.

*

* bits

* [0,1] : fs = 0b01 --> Accelerometer full-scale range selection (+- 0.488 mg/LSB)

* [2,3] : not used.

* [4] : hpf_out = 0 --> high pass filter disabled.

* [5,6,7] : not used

*/

i2c_restart();

i2c_slaveREG_address(XYZ_DATA_CFG_REG); // COLOCA O ENDEREÇO DO REGISTRADOR DO FXOS NO BARRAMENTO DE DADOS

i2c_write(0X02); //ESCREVE NO REGISTRADOR

i2c_stop();

}

/*---------------------------------------------------------------------*/

/* FUNCAO MAIN */

/*---------------------------------------------------------------------*/

int main(void)

{

uart1_init();

i2c_init();

fxos8700cq_init();

i2c_start();

while(1)

{

i2c_restart();

uart1_send( i2c_read());

}

return 0;

}

Maybe someone can give me a clue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Do you have an oscilloscope to see the signals in the PTC3 and PTC4 pins? This just to be sure that the baudrate is ok.

Does the program work ok except for the UART transmissions or does it go to the default handler function?

Also, please enable the clock gate for the PORTC before its initialization.

SIM_SCGC5 |= SIM_SCGC5_PORTC_MASK;

Best regards,

Earl.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Orlando, I enabled PORTC for first and measured UART on the board, PTC = '1' (3.3 V DC) and PTC4 = 10.2 kHz (Square '1'=3.3 V, '0'= 0 V). I try to see Registers values in Debug's window, and UART1_D remain in 0x00. At the begining it went to the default handler function error, now it doesn't write nothing on UART1.

Regards,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Omar,

Does the UART_TX (PTC4) signal completely square or does it seem to be an UART signal? If it seems to be an UART signal maybe the problem is the baudrate. Also, I think that you will see some data in the UART_D register only when you receive data.

Regards,

Earl.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It really seems like a UART signal, do you know the right boudrate configuration I'm using or think I'm using 115200 for UART1_BDH = 0x00 and UART1_BDL = 0x1A. Is it right?

Thanks and regards,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Omar,

In the reference manual you can see that the baudrate is generated as follows:

So the SBR value can be calculated:

SBR[12:0] = UART Module Clock / (16 * Baudrate)

The UART Module Clock is the bus clock which does not seem to be configured.

Best regards,

Earl.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Update:

The UART Module Clock is the bus clock which does not seem to be configured. By default the Bus Clock is 20.97152 MHz, so:

SBR = 20.97152 MHz / (16 * 115200) = 11.3777

I suggest to change the bus clock to 48 MHz, it will produce a more accurate baud rate:

SBR = 48 MHz / (16 * 115200) = 26.0416

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Earl,

I achieved putting the right Baud Rate and the UART has started to function. Now I'm trying to configure right the I2C0 for FX0S7800 reading. UART will serve to have a feedback.

Thanks so much,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi ,

I have just started coding for kl26z board.

I have to use two uarts -lpsci(UART0) and UART1.

Lpsci driver is working fine .I tried writing uart driver for uart1 using the structure of lpsci.

I don't know why uart1 is not working . At first, I tried with pin nos PTE-22 and 23 as given in Pinout schematic .

After going through this conversation ,I changed the pins to PTC3 and PTC4 for Uart1 tx and Rx.

I tried changing the Uart clock but I dont know its not changing and everytime,its showing 12MHZ.

What could be the problem ?

Please suggest me something.