- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: Flexbus initialization and test for external SRAM..?

Re: Flexbus initialization and test for external SRAM..?

Re: Flexbus initialization and test for external SRAM..?

Hi, there is also a similar problem on my device. We have added 512 KB external SRAM to our K60n512 board. The initialization function is the same as described above (as the code from Todd) or in AN4393, except the following

// Set FlexBus Base address for CS0.

FB->CS[0].CSAR = 0x70000000;

// Set CS control register for CS0. Addr s&h, 4 WS, AutoAck, 8bit port.

FB->CS[0].CSCR = FB_CSCR_ASET(1) | FB_CSCR_RDAH(1) | FB_CSCR_WS(4) |

FB_CSCR_AA_MASK | FB_CSCR_PS(1);

// Set FlexBus Base address mask for CS0 and set valid (enable).

FB->CS[0].CSMR = FB_CSMR_BAM(0x07) | FB_CSMR_V_MASK;

When checking FB_CS0 in the oscilloscope while doing some read/write at base address, no signals can be observed from FB_CS0.

It would be appreciated if anyone could provide some possible hints or information about this problem.

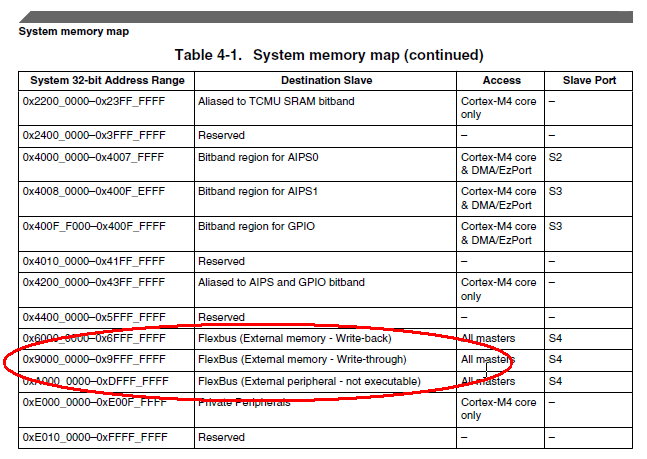

As I know, the flexbus of K60 mapped at the following addresses:

None of them starts from 0x70000000, so would you please try to change FB->CS[0].CSAR to 0x60000000 or 0x90000000 and try again?

Please kindly let me know if the problem is still there.

The problem is solved, CS0 signal can be observed now. After much effort in trying and also checking with hardware designer, we found out it was the following two points that caused the problem:

1. hardware: the address line connection was incorrect on board

2. software: the base address used during read/write was not correctly written, it should be

#define MRAM_START_ADDRESS (*(vuint8*)(0x70000000))

FB_CSAR0 = (uint32)&MRAM_START_ADDRESS;

and when accessing

.....

*(vuint8*)(&MRAM_START_ADDRESS + n) = wdata8;

rdata8=0x00; //clear data variable;

rdata8=(*(vuint8*)(&MRAM_START_ADDRESS + n));

......

Anyway, many thanks for your reply!

I check the Flexbu setting code without any problem.

AN4393 the Flexbus initialization code with below Flexbus clock frequency drivid setting:

SIM_CLKDIV1 |= SIM_CLKDIV1_OUTDIV3(0x0); //FlexBus Clock not divided

Please make sure the Flexbus clock frequency not exceed 50MHz.

Wish it helps.