I am trying to use the FlexCAN module at 500 KBps on a Kinetis MK20DX256ZVLK10. At this time, we do not have an external oscillator connected to the EXTAL/XTAL pins, so I am running the system clock in FEI mode at ~ 20 MHz.

My MQX test application toggles a GPIO pin and repeatedly sends a CAN message once per second. On the K20, I see the GPIO pin toggle (so the app is alive,) but CAN bus spits out only garbage. The same application works fine (both GPIO and CAN) on the TWR-K60N512 dev board. The TWR-K60N512 has an external resonator on the EXTAL/XTAL K60 pins.

I saw the following comment in the "K20 Sub-Family Reference Manual" (document number K20P81M100SF2RM):

p.1136: CANx_CTRL1[CLKSRC] - This bit selects the clock source to the CAN Protocol Engine (PE) to be either the peripheral clock (driven

by the PLL) or the crystal oscillator clock.

Does this mean the _only_ way to use the FlexCAN module is if you have an external oscillator on the K20 EXTAL/XTAL pins?

Thanks for any help.

Ben

已解决! 转到解答。

Referring to the RM:

The FlexCAN module has two clock domains asynchronous to each other:

• The Bus Domain feeds the Control Host Interface (CHI) submodule and is derived

from the peripheral clock.

• The Oscillator Domain feeds the CAN Protocol Engine (PE) submodule and is

derived directly from a crystal oscillator clock, so that very low jitter performance

can be achieved on the CAN bus.

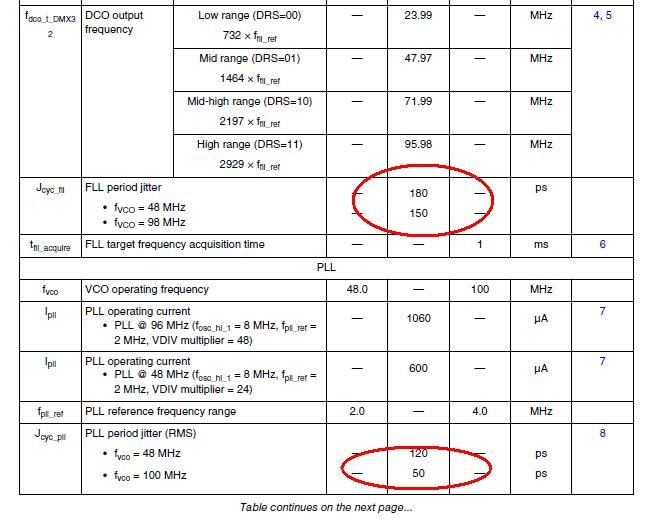

So the ref clock for PE has restriction on jitter, while FLL has a much larger jitter than PLL at the max clock frequency.

so we recommend use PLL or the crystal oscillator clock for PE's source clock, sorry for the inconvenience that has caused.

Referring to the RM:

The FlexCAN module has two clock domains asynchronous to each other:

• The Bus Domain feeds the Control Host Interface (CHI) submodule and is derived

from the peripheral clock.

• The Oscillator Domain feeds the CAN Protocol Engine (PE) submodule and is

derived directly from a crystal oscillator clock, so that very low jitter performance

can be achieved on the CAN bus.

So the ref clock for PE has restriction on jitter, while FLL has a much larger jitter than PLL at the max clock frequency.

so we recommend use PLL or the crystal oscillator clock for PE's source clock, sorry for the inconvenience that has caused.