- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Problem in interfacing ADC with I2S

Problem in interfacing ADC with I2S

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Problem in interfacing ADC with I2S

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone,

I am new to I2S interface and I am trying to interface an ADC to K60 MCU (TWR-K60F512) using I2S interface.

In this case, ADC is always a MASTER, It pumps converted data continuously.

Reading ADC:

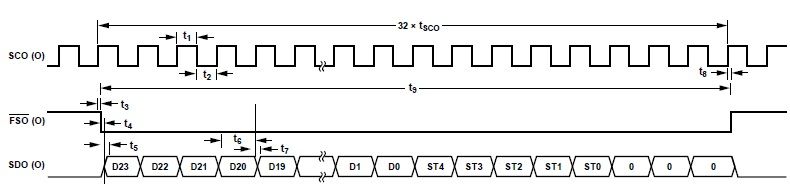

Please see the below timing diagram of ADC, which shows how it transmits the conversion results.

Following are the ADC signals related to ADC Read :

a) Serial Clock Output (SCO),

b) Frame Synchronization Output (FSO)

c) Serial Data Output (SDO)

- The data read from ADC is clocked out using Serial Clock Output(SCO).

- The conversion result output on the SDO line is framed by the frame synchronization output FSO, which is sent logic low for 32 SCO cycles.

- Each bit of the new conversion result is clocked onto SDO line on the rising SCO edge and is valid on the falling SCO edge.

- The 32-bit result consists of 24 data bits followed by 8 status bits.

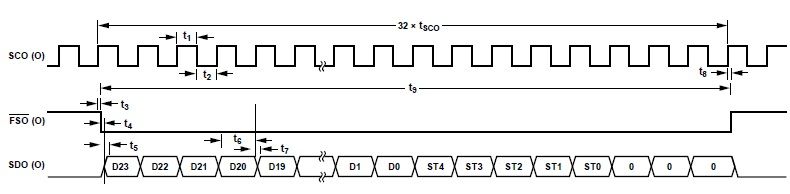

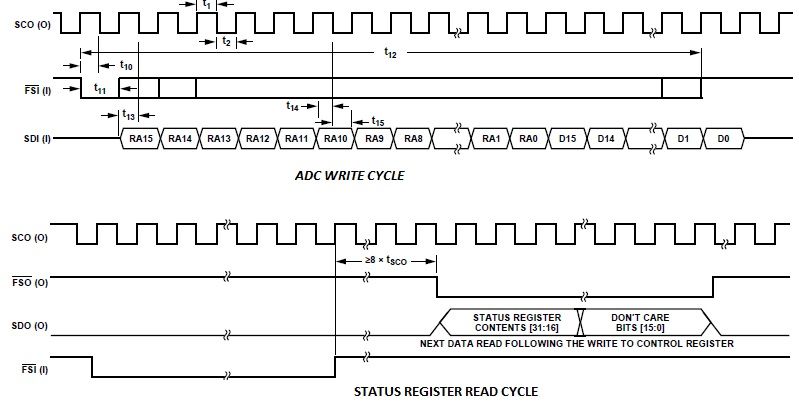

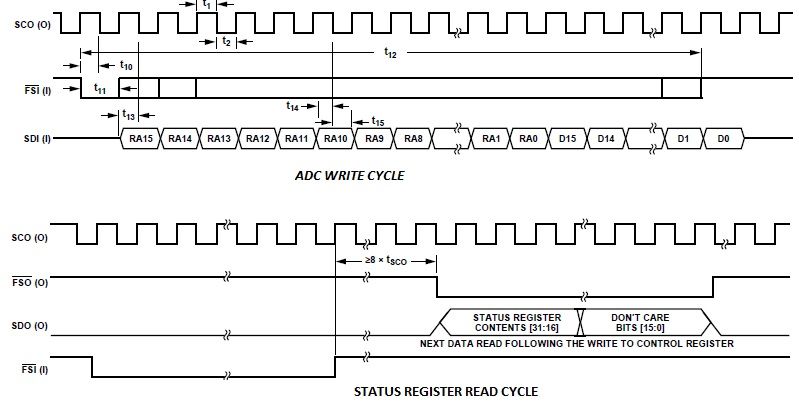

Writing ADC:Please see the below timing diagram of ADC which shows how a write operation is performed.

- Serial writing operation is synchronous to SCO signal.

- The status of the FSI is checked on the falling edge of the SCO signal. If FSI line is low, then first data bit on the SDI line is latched on the next SCO falling edge.

- FSI signal is made low at a position when SCO signal is high or low to allow setup and hold times from the SCO falling edge to be met.

- The width of the FSI signal can be set to between 1 and 32 SCO periods wide.

- Write data is pumped onto SDI with sync to SCO.

- A second or subsequent falling edge that occurs before 32 SCO periods have elapsed is ignored.

For this requirement, I planned to interface ADC to I2S module as follows:

SCO -> I2S0_RX_BCLK, I2S_TX_BCLK

FSO -> I2S0_RX_FS

SDO -> I2S0_RX_D0

FSI <- I2S0_TX_FS

SDI <- I2S0_TX_D0

void main (void)

{

char ch;

printf("\nHello World!!\n");

enable_irq(35); //I2S0 Transmit IRQ

enable_irq(36); //I2S0 Receiver IRQ

init_i2s();

while(1);

}

void init_i2s(void)

{

// /* Turn on all port clocks */

SIM_SCGC5 = SIM_SCGC5_PORTA_MASK | SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTC_MASK | SIM_SCGC5_PORTD_MASK | SIM_SCGC5_PORTE_MASK;

//

// SIM_SCGC6 |= SIM_SCGC6_SAI0_MASK;

//

// PORTC_PCR(3) = PORT_PCR_MUX(6); //PTC3(ALT6), I2S0_TX_BCLK - J53 pin11

// PORTC_PCR(2) = PORT_PCR_MUX(6); //PTC2(ALT6), I2S0_TX_FS - J8 pin8

// PORTC_PCR(9) = PORT_PCR_MUX(4); //PTC9(ALT4), I2S0_RX_BCLK - J6 pin5

// PORTC_PCR(10) = PORT_PCR_MUX(4); //PTC10(ALT4), I2S0_RX_FS - J6 pin2

// PORTC_PCR(5) = PORT_PCR_MUX(4); //PTC5(ALT4), I2S0_RXD0 - J8 pin2

// PORTC_PCR(11) = PORT_PCR_MUX(4); //PTC11(ALT6), I2S0_RXD1 - J14 pin8

// PORTC_PCR(1) = PORT_PCR_MUX(6); //PTC1(ALT6), I2S0_TXD0 - J8 pin11

// PORTC_PCR(0) = PORT_PCR_MUX(6); //PTC0(ALT6), I2S0_TXD1 - J8 pin14

// PORTC_PCR(6) = PORT_PCR_MUX(6); //PTC6(ALT6), I2S0_MCLK - J6 pin14

SIM_SCGC6|=0x00008000;

PORTC_PCR6= (0|PORT_PCR_MUX(6)); //MCLK

PORTC_PCR3= (0|PORT_PCR_MUX(6)); //Tx_BCLK

PORTC_PCR2= (0|PORT_PCR_MUX(6)); //Tx_FS

PORTC_PCR1= (0|PORT_PCR_MUX(6)); //Tx_D0

PORTC_PCR9= (0|PORT_PCR_MUX(4)); //Rx_BCLK

PORTC_PCR10=(0|PORT_PCR_MUX(4)); //Rx_FS

PORTC_PCR5= (0|PORT_PCR_MUX(4)); //Rx_D0

I2S0_MCR=0x00000000;

I2S0_MDR=0x00000000;

I2S0_RCR1=0x00000007;//FIFO watermark level

I2S0_RCR2=0xC0000000;//mode, mclk, bit clock settings

I2S0_RCR3=0x00010000;//channel num, word flag config.

I2S0_RCR4=0x00001F12;//Frame config-pol,dir,size,width..

I2S0_RCR5=0x1F1F1F00;//word config..

I2S0_RMR =0x00000000;//Word Mask Register, all are enabled

I2S0_RCSR=0x931C1F00;

}

void i2s_rx_isr(void)

{

// I2S0_RCSR|=(I2S_RCSR_SEF_MASK|I2S_RCSR_FRF_MASK);

GPIOB_PTOR|=GPIO_PDOR_PDO(GPIO_PIN(23)); //toggle port pin to ensure the occurrence of Interrupt

I2S0_RCSR |= 0x02380000;

}

I am not getting any interrupt.

Please review the configuration and the corresponding code. Please correct the configuration settings and code as required in the timing diagram.

Thanks in advance

Gourah

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Gourah,

As I've already mentioned in I2S interface , this configuration can't be set with SAI module (Receiver can be configured without problems but Transmitter can't synchronize FCLK signal if he is receiving Master clock from Slave.)

If you still are interested in configure SAI module you can check this example code (using I2S for audio interface with SGTL5000 codec) Re: is there any demo code for using I2S? or you can take a look to FlexIO module in this post: Understanding FlexIO

I hope this can help you

Best Regards,

Isaac