- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Kinetis SAI module

Kinetis SAI module

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Kinetis SAI module

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Customer plans to feed I2S audio stream that consists of both left/right channel audio data into K22, and the FW is expected to perform some rudimentary processing on the raw I2S data received. This processing must be done independently for left and right channel, so obviously the first task is to be able to separate the left channel data from the right channel.

Looking at the K22 spec, the SAI module provides two receive data pins (SAI_RXDATA0 and SAI_RXDATA1), and that there are also two receive data registers (I2S0RDR0, I2S0_RDR1), so the customer assume each pin has its own dedicated receive register. They want to feed the incoming I2S audio stream into both pins, but mask out the left channel data on one path and right channel on the other path, so that one receive data register will only get left channel data and the other only right channel data. However, it looks like there is only one instance of receive mask register. So does that mean whatever value they program into that mask register will identically affect both receive paths?

Are there any appnotes related to SAI module?

Regards,

hy

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, HyMaim

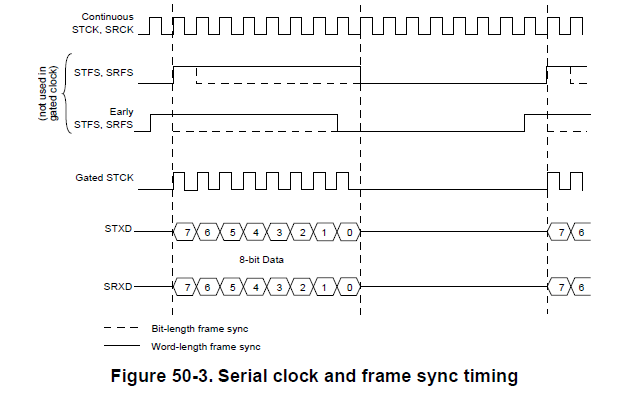

Unfortunately, your concept about the left/right channels is incorrect. Each receiving pin of I2S for example SAI_RXDATA0 can receive both the left channel and right channel, for example the following fig demostrates the I2S protocol, each frame include two slots, when the SFRS(Serial receive frame Sync) is high, it is slot0 or left channel, you get the left channel data for example, when the SFRS is low, it is second slot or right channel, you get the right channel.

This is the procedure to get the I2S receiving data, when the I2S module recieved data, the FRF bit is set, if you enable interrupt, an interrupt is triggered, in the ISR, you can read the FIFO to a buffer, it is okay.

Regarding the left/right channel, in the receiving ISR, you can check the WSF bit in the I2Sx_RCSR to know if the received data is the first slot data or second slot data if you disable FIFO feature. But if you use FIFO mode, if the FIFO size is greater than the watermark, an interrupt can be generated, you can read multiple data from FIFO, in the case, the WSF bit is meaningless. In the FIFO mode, you can enable the Word start interrupt by setting the WSIE bit, in the ISR, you can empty the FIFO, then clear WSIE bit, so that you know that the next data in the FIFO is the first slot data. After you know the first slot data, all the following received data will be in interleaved, slot0 data/slot1 data/slot0 data/slot1 data/........., you can save the slot0 to one buffer, slot1 data to another buffer.

As you know that the received FIFO data is interleaved, it is a bit difficult to identify the left channel data or right channel data.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Xiangjun,

I hope I address your first name correctly. Thx for your quick reply.

Regarding the SAI Receive Mask Register (I2S0_RMR), it appears there is only one copy of this register, so if I program it to mask out either slot0 or slot1 data, would it affect both Receive Data Registers identically?

Regards,

hy

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Hymai,

If you use I2S protocol which only consists of two slots, in the case, you should clear bit0 and bit1 in I2S0_RMR, in the setting, the both the received data in both slot0 and slot1 are copied to the I2Sx_RDR0 register, it is okay.

For K22, there are two data input pins:SAI_RX_DATA0 and SAI_RX_DATA1, and there are two data register I2Sx_RDR0 and I2Sx_RDR1, because there is only one I2S0_RMR register, the slot setting functions for both SAI_RX_DATA0 and SAI_RX_DATA1.

Hope it can help you

BR

XiangJun Rong