- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: KBI Interrupt on KE02

KBI Interrupt on KE02

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am attempting to use the KBI0, Pin 1 Interrupt on a KE02Z processor.

I am using Kinetis Design Studio 3.2.0 with Processor Expert version shown below:

The KBI Processor Expert (Sync_Int:init_KBI) component looks like this:

and appears to be a bit incomplete.

I've modified/added-to the automatically-generated code and here's what I have so far:

/*

** ===================================================================

** Method : Sync_Int_Init (component Init_KBI)

** Description :

** This method initializes registers of the KBI module

** according to the Peripheral Initialization settings.

** Call this method in user code to initialize the module. By

** default, the method is called by PE automatically; see "Call

** Init method" property of the component for more details.

** Parameters : None

** Returns : Nothing

** ===================================================================

*/

void Sync_Int_Init(void)

{

// Connect system clock to KBI0 module (not well documented)

SIM_SCGC |= SIM_SCGC_KBI0_MASK;

/* KBI0_SC: ??=0,??=0,??=0,??=0,KBF=0,KBACK=0,KBIE=0,KBMOD=0 */

KBI0_SC = 0x00;

/* KBI0_ES: KBEDG=2 */

KBI0_ES = KBI_ES_KBEDG(0x02);

/* KBI0_PE: KBIPE=2 */

KBI0_PE = KBI_PE_KBIPE(0x02);

/* KBI0_SC: KBACK=1 */

KBI0_SC |= KBI_SC_KBACK_MASK;

/* KBI0_SC: KBIE=1 */

KBI0_SC |= KBI_SC_KBIE_MASK;

}

/*

** ###################################################################

**

** The interrupt service routine(s) must be implemented

** by user in one of the following user modules.

**

** If the "Generate ISR" option is enabled, Processor Expert generates

** ISR templates in the CPU event module.

**

** User modules:

** main.c

** Events.c

**

** ###################################################################

** */

PE_ISR(Sync_Interrupt)

{

/* KBI0_SC: KBIE=1 */

KBI0_SC |= KBI_SC_KBACK_MASK;

... <my code here>

}

I can download the code and KBI seems to initialize ok, but the ISR is never called.

I found this post:

which (at the end of the reply) references NVIC_ICER and NVIC_IPER6. I see documentation on the second register - just a place to set the interrupt priority. But what is NVIC_ICER? I don't see that even mentioned in the reference manual. Is there a bit in that register that turns on the KBI interrupt?

Thanks in advance for any insight you can provide.

~LMG

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

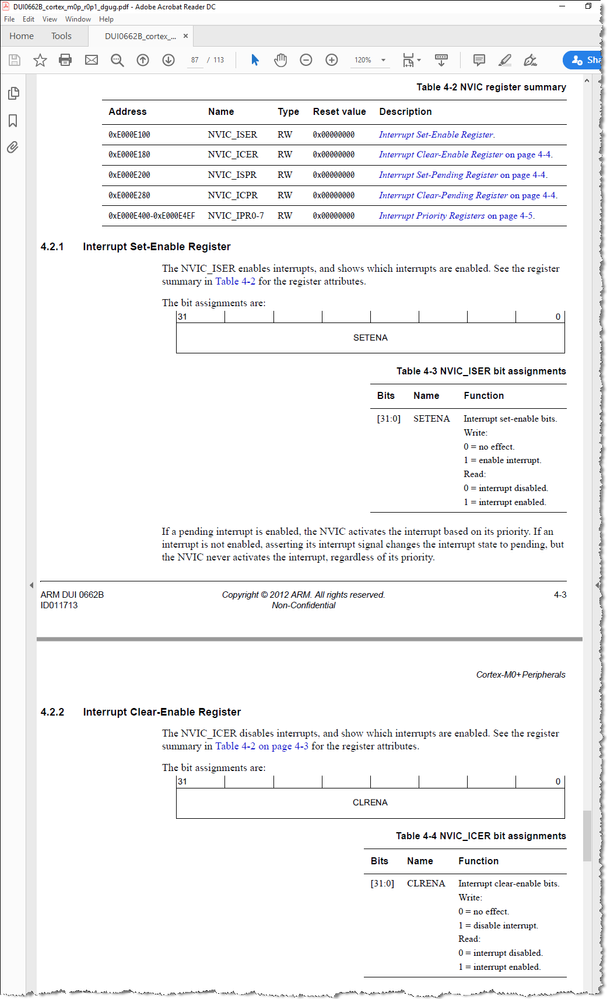

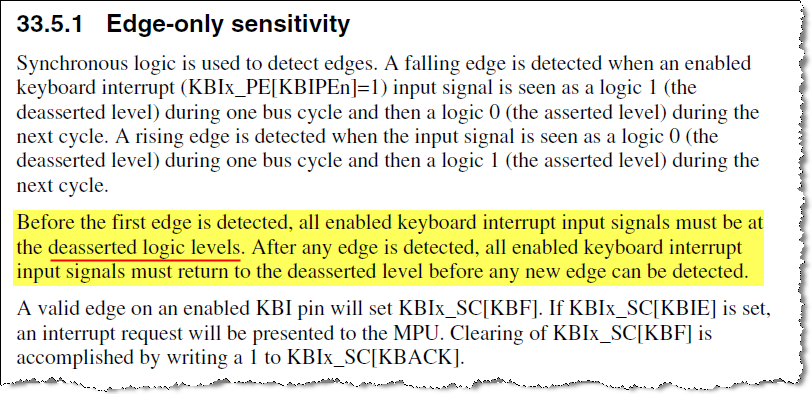

Here is the NVIC register summary, see NVIC_ISER and NVIC_ICER:

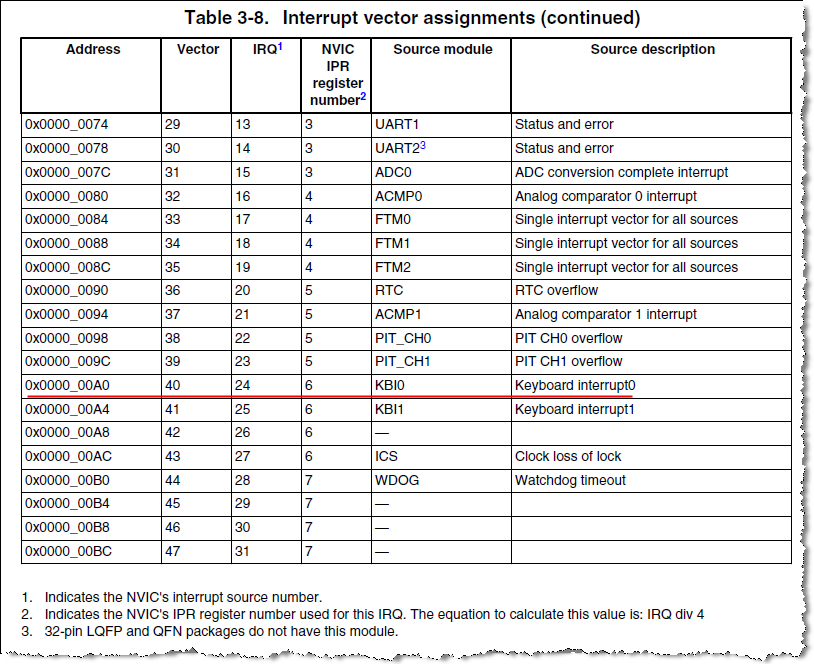

The Interrupt vector assignments of KBI0 in KE02 are same as KE04, you can use the codes in that post.

From your codes, rising edge is configured for this pin. Did you enable internal pull-down or put external pull-down for KBI0 pin1?

Here the "deasserted logic levels" is 0v for your configuration.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Here is the NVIC register summary, see NVIC_ISER and NVIC_ICER:

The Interrupt vector assignments of KBI0 in KE02 are same as KE04, you can use the codes in that post.

From your codes, rising edge is configured for this pin. Did you enable internal pull-down or put external pull-down for KBI0 pin1?

Here the "deasserted logic levels" is 0v for your configuration.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks! Very helpful summary.

~LMG

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

See the ARM core documentation, which is not included in the user's manual: http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0662b/Cihbiadi.html

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]