- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- IMXRT1024 LPUART, eDMA and OCRAM Relationship

IMXRT1024 LPUART, eDMA and OCRAM Relationship

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IMXRT1024 LPUART, eDMA and OCRAM Relationship

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all,

I am stuck with a relationship triangle (LPUART, eDMA, ADMA and OCRAM). I just want to use eDMA with LPUART and trying to monitor my transmit and receive datas on the RAM. Here is my nested path from Reference Manual.

In 6.2 Overview it says:

Local memory containing transfer control descriptors for each of the 32 channels

In 6.2.3 Features it says:

TCD supports two-deep, nested transfer operations

• 32-byte TCD stored in local memory for each channel

• An inner data transfer loop defined by a minor byte transfer count

• An outer data transfer loop defined by a major iteration count

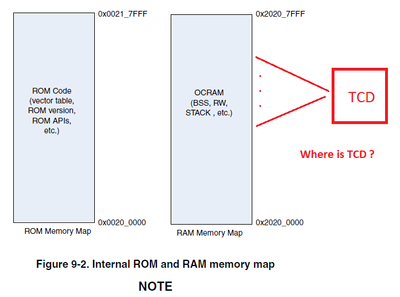

In Figure 9-2. Internal ROM and RAM memory map NOTE it says:

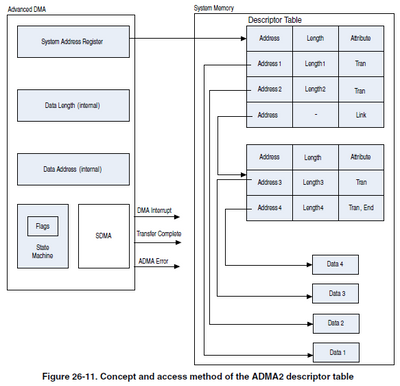

In Figure 26-11. Concept and access method of the ADMA2 descriptor table it says:

So I have following question:

Q1: What is the difference between eDMA and ADMA?

Q2: Where will create my eDMA's TCD in the memory(RAM)? So, Which address interval?

Q3: How can I monitor my eDMA LPUART receive and transmit datas on RAM in MCUExpresso IDE in debug time?

Thanks and Regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas_Frank,

I see that some of your questions have been answered on other threads. I’m adding a link for reference in case it helps other users.

https://community.nxp.com/t5/i-MX-RT/IMXRT1024-LPUART-eDMA-RAM-Location-and-Limitation/m-p/1329191

I think the matter that was not covered would be the differences between eDMA and ADMA. The Advanced DMA (ADMA) is a transfer algorithm used by the SD Host Controller so it’s a different DMA algorithm. There are more details on how it’s handled on the i.MXRT1024 Reference Manual on the uSDHC chapter as it’s main application is being compliant with the uSDHC standard.

Regards,

Gustavo