- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: I2S slave frame sync problem MK10DX128VLL7 PE SSI

I2S slave frame sync problem MK10DX128VLL7 PE SSI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2S slave frame sync problem MK10DX128VLL7 PE SSI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

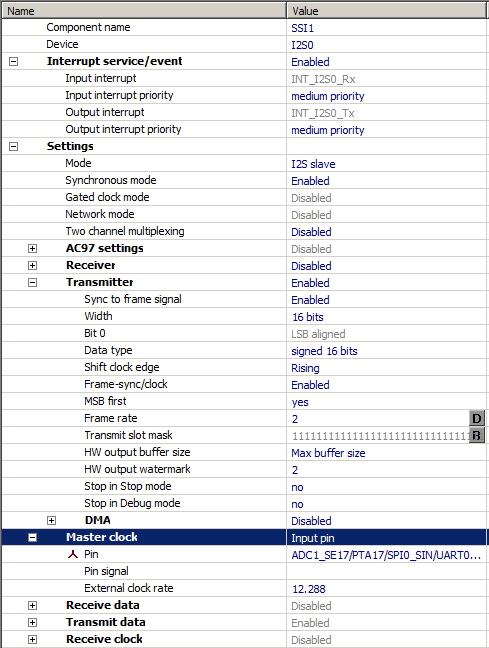

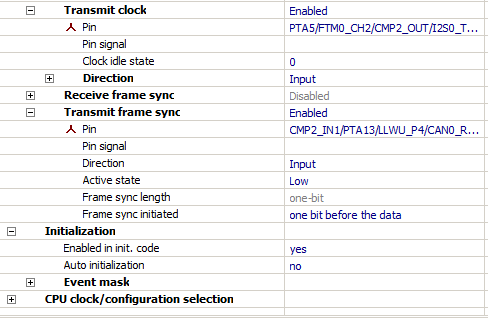

I am trying to communicate with WM8956 codec over I2S. I2S slave mcu is MK10DX128VLL7. I use processor expert v10.5.1, CodeWorrior 10.5.

WM8956 is I2S master sends TX_BCLK and TX_FS

MK10DX128VLL7 is I2S slave sends TX_Data

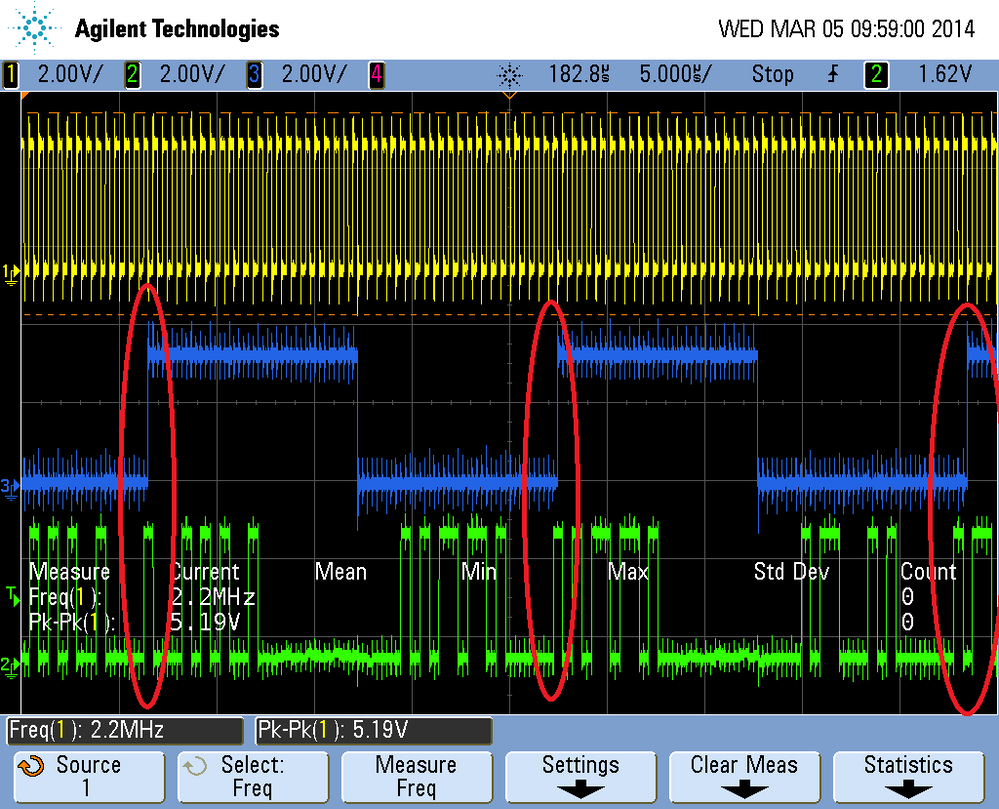

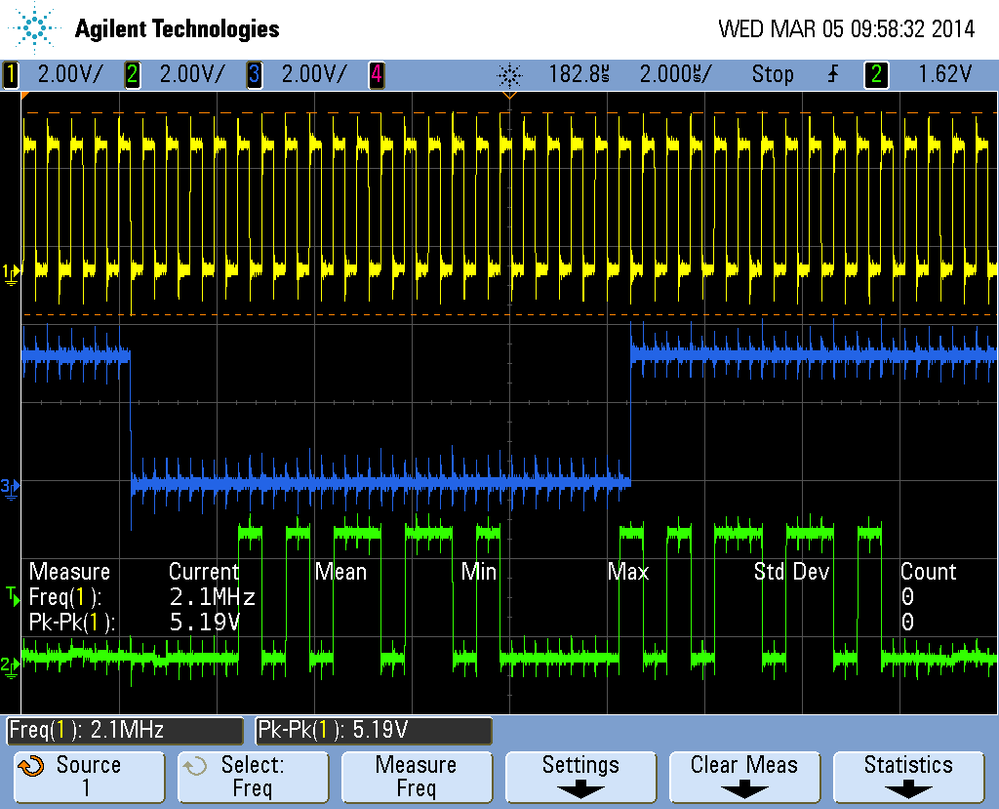

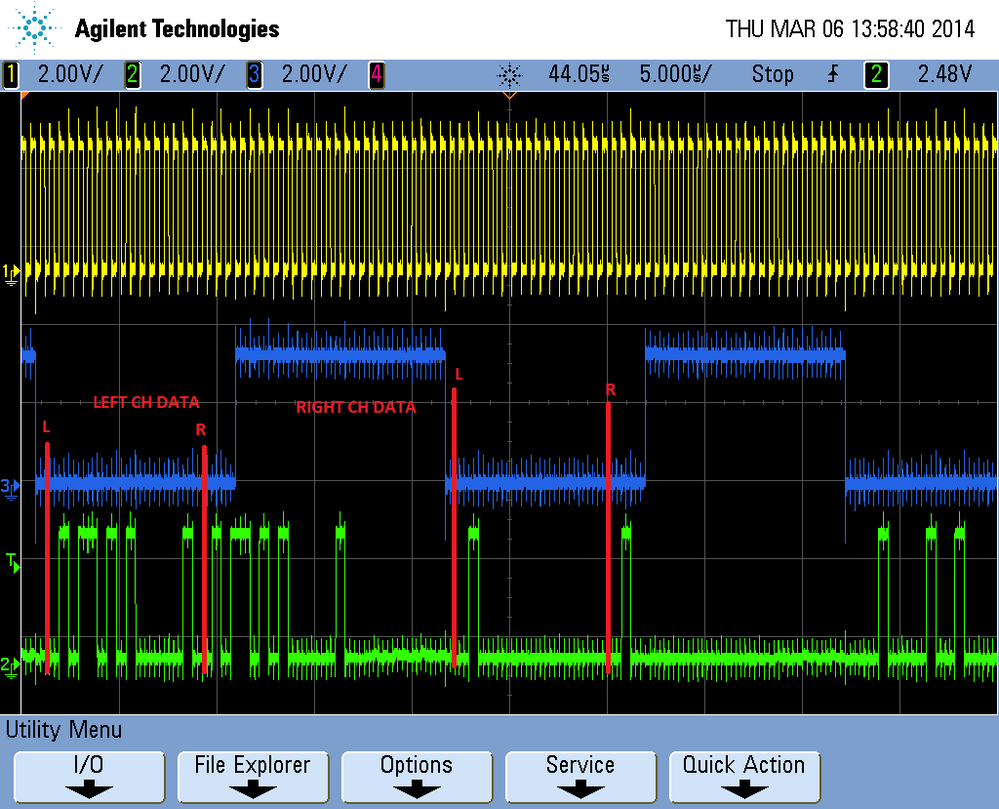

Yellow: TX_BCLK

Blue: TX_FS frame sync

Green: TX_data (send from kinetis)

I want to send 16bit data for each left and right channels. You can send 21bit for one channel in my clocking configuration. After frame sync signal is changed, TX_data should be like that first bit is empty next 16bits are data and last 4 bits should be empty. But as you can see from the scopes below highlighted with red circuls, there are changes while 4 last bits. So I think MCU does not try to sync with Frame Sych signal.

My processor expert properties are also attached. Please give a suggestion...

Thank you...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As you have said, the SAI module of K10 works in slave mode, the bit clock and frame clock TX_BCLK and TX_FS are from external device. From the waveform of scope, obviously, the frame clock signal TX_FS is a word clock rather than a bit clock, but in the PE beans, you select "Transmit frame sync"->"Frame sync length" as one-bit clock, it should be "one-word", at least, this is a issue, pls check the SYWD bits in the I2Sx_TCR4 register, it should be 01111 in binary. pls try to change it.

I have counted the clock number the TX_FS covers within High logic, it seems the number is 21 rather than 16, are you sure it is correct?

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

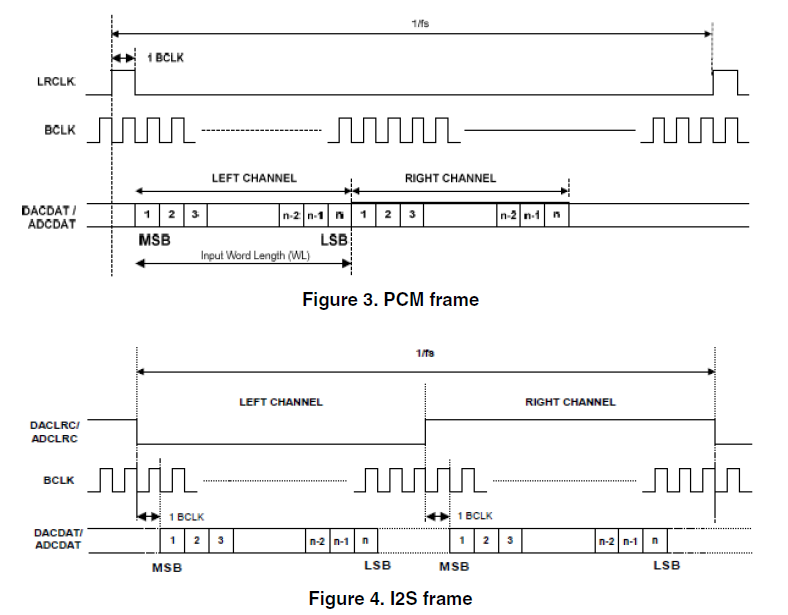

Hi, now I send same data for left channel and right channel to better understand FS signal and TX_DATA. What I saw is that for right channel SAI does not wait FrameSync signal to go high. It appends right channel data to left channel. AN4800 document explains PCM and I2S signals, you can see a copy below. PE I2S slave TX_data signal looks like PCM data signal.

I tried to change SYWD bits( from generated code because it is grayed out in PE ) as you suggested and I also tried the values 20,21 but nothing changed.

Probably I have to use my codec in PCM mode.

figure: AN4800 page3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Okan,

I have downloaded the data sheet of WM8596, from Table 38, all says that the BCLK runs at 64*Fs, FS is the sampling frequency, which means that slot number is always 32 bits, in other words, the High logic of frame clock covers 32 BCLK cycles. But your scope shows it is 21, i think the setting of WM8596 is not correct.

As a test, could you configure the DAC as a slave, sai of K10 is the master, use 32 BCLK for each slot, use 24 bits data(8 bits data is useless), one word frame clock, frame clock is early one bit. In this way, you can see the timing of sai of k10.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun,

I actually solve problem by running WM8596 in PCM mode since K10 send second channel data right after first one. According to I2S protocol second channel data should be send after rising edge of FS. and FS should cover all the data bits but it can be longer than a word. What I mean is that if you want to send 16bits word for a channel FS low time or high time can be greater than 16bits there is no restriction about how much greater. I get this idea from AN4800 page 3 and google search, of course I am not 100 percent sure. Thank you for your help...

Okan ERCAN