- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: How to load usb stack to DDR memory

How to load usb stack to DDR memory

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How to load usb stack to DDR memory

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @abhilash did you get the USB stack to work fine from DDR? Would you be kind enough to attach it here ? We are facing the very same issue. It runs fine in Flash, but the DDR build just won't work. We've tried everything from changes in linker file to tcl script to watchdog. Your project will really help us. Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The released demo just support flash and RAM target, but I think you may use the RAM target as a starting point.

The main differences with a standard “RAM target” are :

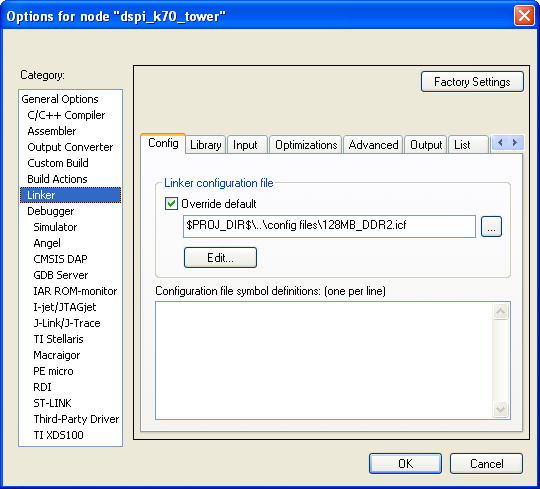

− Appropriate linker file

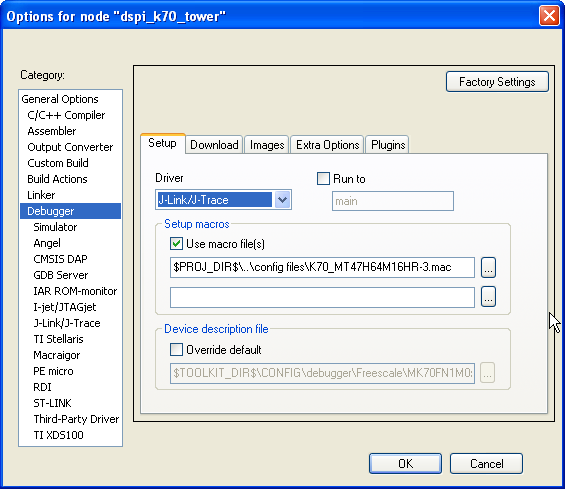

− Macro set-up file that initializes the DRAM chip before the J-link starts download.

they can be both referred to 128MB_DDR2.icf from KINETIS_120MHZ_SC, and K70_MT47H64M16HR-3.mac as well.

Please kindly refer to the following for details.

Hope that helps,

B.R

Kan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for the information

Kan

I followed your instruction and used linker files from KINETIS_120MHZ_SC for DDR(128MB_ddr.lcf) and ram(MK70FN1M0_ram.lcf). Also we are using initialization file for the DDR (init_twr_k70_ddr2.tcl). But when i loaded and started running the program it exits when TestApp_Init(); function is called .The program runs fine when run from flash memory.

{ I am running USB stack 4.1.1 CDC sample program in High speed config using code warrior IDE10.2 and OSJTAG downloader }

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As I know, K70 has two PLLs , PLL1 is dedicated for DDR , and PLL0's output can be used for USB module, I am not sure how you configure them, but in my opinion , PLL0 should output 48MHz for USB application, PLL1 may output as high as possible to meet the DDR2 spec. so please check the PLL initialization first.

Hope that helps,

B.R

Kan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hello kan,

inside the init file pll1 is configured and it is used for ddr configuration. when using DDR memory Sysinit function is not working.For now i have it disabled. Now my doubt is on the linker file . Is there any specific linker file that can be used with USB stack

thanks

Abhi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Abhi,

Sorry for the late response!! I had some issue with my IAR license until I re-installed it. I have implemented the CDC demo running in DDR based on TWR-K70, but It is not only the link file, but also the PLL init function called in the usb stack should be modified to make the usb stack run in DDR.

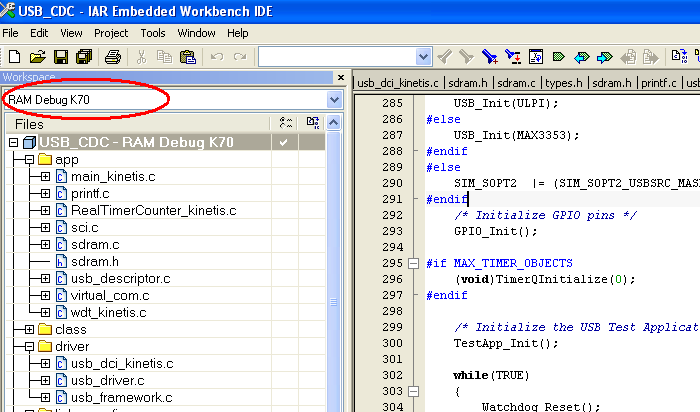

First , I recommend you start with a SRAM target configuration,

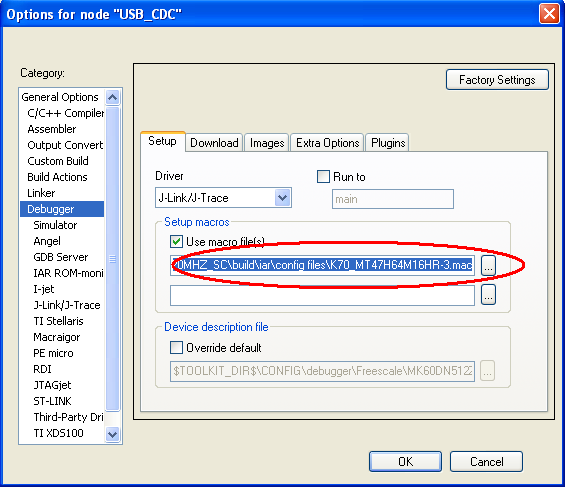

second, just as mentioned before, use mac file to initialize the PLL0 and PLL1 as well as the DDR controller before the IDE load the image.

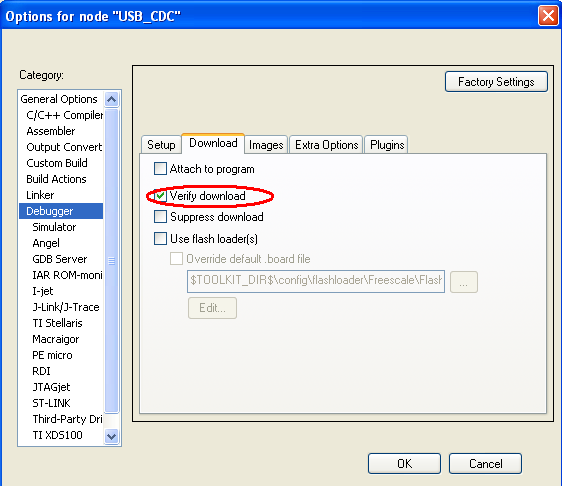

and choose verify download if you like

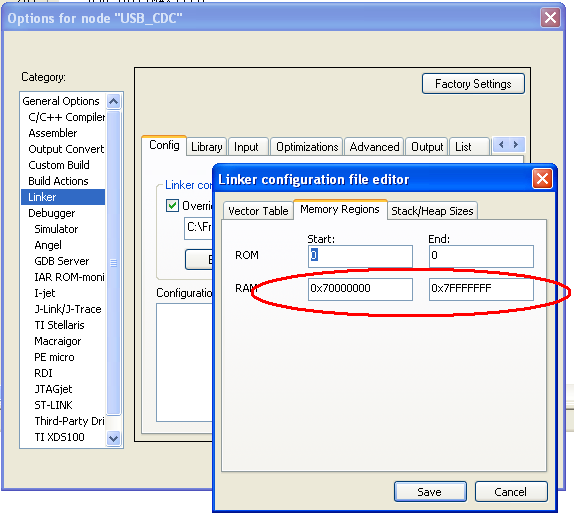

then, you may change the sram link file as the following:

you may find the RAM section are in DDR now, but please note don't set 0x08000000 to 0x10000000 as the range, this configuration are used by KINETIS120MHZ_SC, but as the USB stack uses DMA to transmit or receive data, you have to put the section in a location that allow access from both core and eDMA.

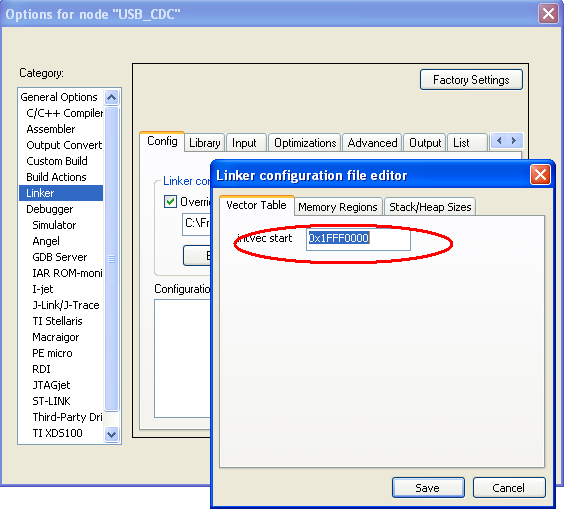

and set the vector table in SRAM.

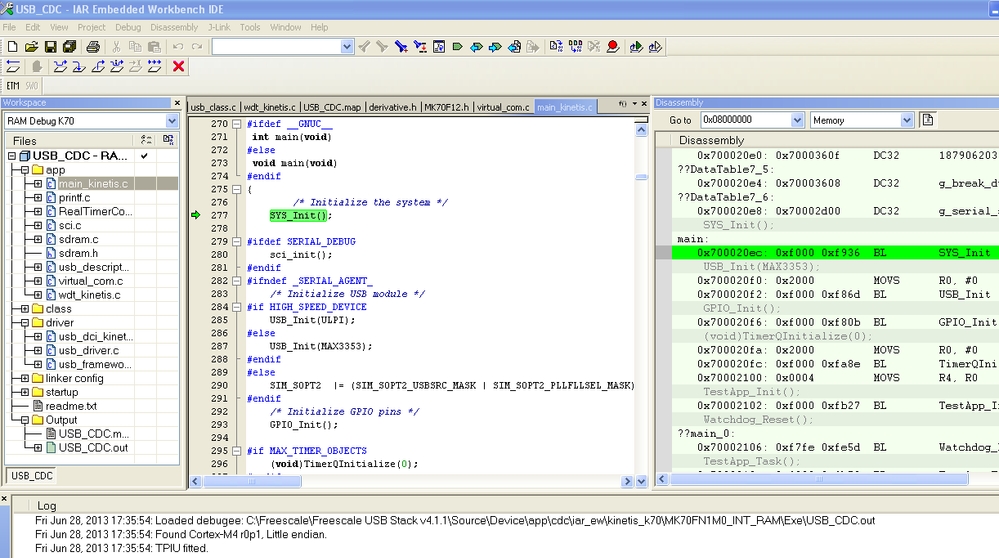

As PLL0 and PLL1 have been initialized in the mac file, there is no need to do it in SYS_Init(), add some code from line 884 in main_kinetis,c

#ifdef SDRAM

/* Initialize clocks to match values from init script */

mcg_clk_hz = 120000000;

pll_1_clk_khz = 150000;

pll_0_clk_khz = mcg_clk_hz / 1000;

#else

#define ASYNCH_MODE /* PLL1 is source for MCGCLKOUT and DDR controller */

#define SDRAM

and #endif at line 924.

Define SDRAM in "derivative,h "

#define SDRAM

After that, run the application , you will see the following view:

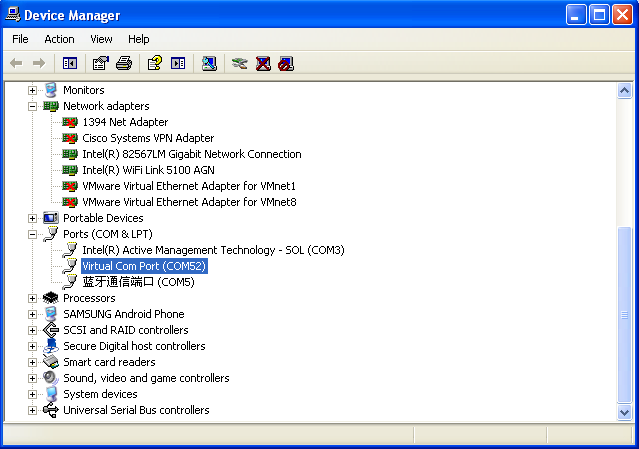

and found the cdc device in the device manager:

Hope that helps,

Have a nice weekend!!

B.R

Kan