- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: How to do the clock initialization

How to do the clock initialization

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to do the clock initialization

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How to initialize the clock for MK24F12(kinetic controller) in IAR workbench.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

If you want to understand MCG details check out http://www.utasker.com/kinetis/MCG.html

Code for TWR-K24F120M is included in https://github.com/uTasker/uTasker-Kinetis

Assuming you want to use the PLL to generate 120MHz (and max. speed clocks) the configuration is:

#define OSC_LOW_GAIN_MODE // use low gain oscillator mode since there is not crystal loading in the circuit

#define CRYSTAL_FREQUENCY 8000000 // 8 MHz crystal

#define _EXTERNAL_CLOCK CRYSTAL_FREQUENCY

#define CLOCK_DIV 2 // input must be divided to 2MHz..4MHz range (/1 to /24)

#define CLOCK_MUL 30 // the PLL multiplication factor to achieve operating frequency of 120MHz (x24 to x55 possible)

#define FLEX_CLOCK_DIVIDE 3 // 120/3 to give 40MHz

#define FLASH_CLOCK_DIVIDE 5 // 120/5 to give 24MHz

Code for this is (not IAR specific because compatible with all compilers):

MCG_C1 = (MCG_C1_CLKS_EXTERN_CLK | MCG_C1_FRDIV_VALUE); // switch to external source (the FLL input clock is set to as close to its input range as possible, although this is not absolutely necessary if the FLL will not be used)

while ((MCG_S & MCG_S_OSCINIT) == 0) { // loop until the crystal source has been selected

}

while ((MCG_S & MCG_S_IREFST) != 0) { // loop until the FLL source is no longer the internal reference clock

}

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_EXTERN_CLK) { // loop until the external reference clock source is valid

}

MCG_C5 = ((CLOCK_DIV - 1) | MCG_C5_PLLSTEN0); // now move from state FEE to state PBE (or FBE) PLL remains enabled in normal stop modes

MCG_C6 = ((CLOCK_MUL - MCG_C6_VDIV0_LOWEST) | MCG_C6_PLLS); // set the PLL multiplication factor

while ((MCG_S & MCG_S_PLLST) == 0) { // loop until the PLLS clock source becomes valid

}

while ((MCG_S & MCG_S_LOCK) == 0) { // loop until PLL locks

}

SIM_CLKDIV1 = (((SYSTEM_CLOCK_DIVIDE - 1) << 28) | ((BUS_CLOCK_DIVIDE - 1) << 24) | ((FLEX_CLOCK_DIVIDE - 1) << 20) | ((FLASH_CLOCK_DIVIDE - 1) << 16)); // prepare bus clock divides

MCG_C1 = (MCG_C1_CLKS_PLL_FLL | MCG_C1_FRDIV_1024); // finally move from PBE to PEE mode - switch to PLL clock

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_PLL) { // loop until the PLL clock is selected

}

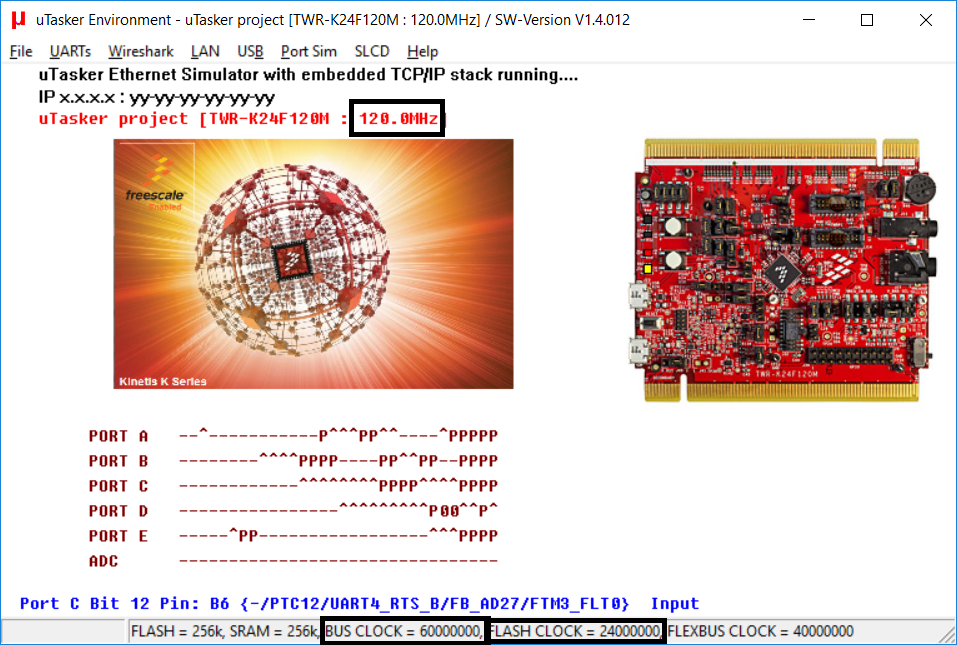

Simulation, showing clock speeds achieved:

Regards

Mark

Complete Kinetis solutions for professional needs, training and support: http://www.utasker.com/kinetis.html

Kinetis K21/K22/K24:

- http://www.utasker.com/kinetis/TWR-K21D50M.html

- http://www.utasker.com/kinetis/TWR-K21F120M.html

- http://www.utasker.com/kinetis/FRDM-K22F.html

- http://www.utasker.com/kinetis/TWR-K22F120M.html

- http://www.utasker.com/kinetis/BLAZE_K22.html

- http://www.utasker.com/kinetis/tinyK22.html

- http://www.utasker.com/kinetis/TWR-K24F120M.html