- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: How long is the default bus frequency?

How long is the default bus frequency?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How long is the default bus frequency?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

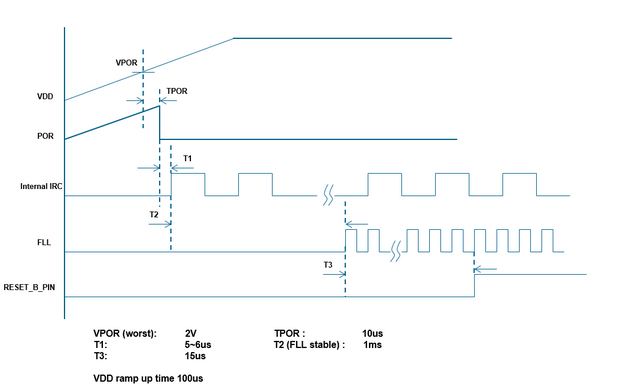

Using MK20DN512VMD10, on a POR or the assertion of RESET (while powered) what is the bus clock frequency? Using register defaults I believe it to be 20.19MHz. This question arose after reading section '6.2.4 Reset Pin' in the reference manual about RESET being active for at least 128 bus clock cycles. Can this time occur before VDD reaches 3.3V?

thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi MARK BRINKMAN,

In default, the MK20DN512VMD10 is using the 32.768 IRC as the clock source, the clock mode is FEI, FLL default factor is 640.

So, the default bus clock is 32.768*640=20.971Mhz.

About the POR sequence, you can refer to this post, there has a picture, you can know the detail kinetis POR sequence, FLL working and the reset pin relationship.

https://community.nxp.com/docs/DOC-332014

Wish it helps you!

If you still have question, please let me known.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Kerry,

I think you meant 20.971MHz instead of 20.971KHz

I do have follow up questions:

1. The post you referenced states that initialization takes place after the Reset_b pin is released while the following section in the MK20DN512VMD10 reference manual states that internal initialization is done while the Reset_b pin is asserted. Can you explain this contradiction?

2. To be clear the duration of the aforementioned 128 bus clock cycles, at 20.971MHz, is at least 6.1us. Is this time part of T3 in the posts picture?

Thanks

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark Brinkman,

Yes, it is 20.971MHz, my mistyping.

You can consider the T3 on the above picture should be at least 128 bus clock cycles.

That document is from the KE series. in the K series, please refer to the reference manual, the RESET pin is driven low by the MCU for at least 128 bus clock cycles and until flash

initialization has completed.

The picture is give your a reference. You can consider T3 should at least 128 bus clock, it is for the flash initialization.

Wish it helps you!

If you still have question, please let me know!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------