- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Getting same ADC value on FRDM-KL43Z freedom board.

Getting same ADC value on FRDM-KL43Z freedom board.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Getting same ADC value on FRDM-KL43Z freedom board.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

We want to use ADC operation of KL17 in our project. We are requiring ADC operation for mutilple analog inputs.

Since in KL17 we can perform ADC operation for only one channel at a time, we are doing ADC operation for next channel once first channel's ADC conversion is done. The next ADC channel is selected by writing SC1A register in Interrupt routine of first conversion.

ADC0 is configured as follows -

1) ADC0 is used as single ended 10 bit conversion mode with normal power configuration and long sample time disabled .

2) Input clock is selected as bus clock with divide ratio of 1.

3) ADC trigger is selected as software trigger.

4) Volatage reference source selected as external reference voltage source - VREFH and VREFL.

Following are the registers configured before triggering ADC conversion -

SIM_SCGC6 - Set bit 27 of this SFR to enable ADC0 clock gate.

ADC0_CFG1 - 0x00000008 //Normal powered ADC

//Clock source selected as input bus clock with devide ratio of 1

//Short sample time

//10 bit single ended ADC operation

ADC0_SC2 - 0x00000000 //Select ADC trigger as software trigger

//Disable compare function

//Select ADC reference voltage source as defualt voltage reference source i.e. VREFH and //VREFL

ADC0_SC3 - 0x00000000 //SC3 register feature are not used thus keeping its value 0.

Then write ADC0_CFG2 register to select channel a or b and then trigger the ADC operation by writing ADC0_SC1A register for first channel.

Selecting next channel and triggering ADC conversion for next channel is handled in Interrupt routine of ADC conversion.

We are trying to test this ADC functionality on FRDM-KL43Z freedom board but we are facing following problem -

Either we provide or not provide some input on analog pin -

For all channels, we are getting ADC value as 1023 if VREFH is not provided by keeping jumper J19 open .

For all channels, we are getting ADC value between 550 - 600 if VREFH is provided by shorting J19 jumper.

Could you please tell why we are facing above problem and not getting exact ADC value for individual channels ?

Are we missing something in ADC configuration or to test on FRDM-KL43Z freedom board?

Thanks and Regards,

Vinayak Wadkar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Yes you are correct, the pin 7 of J4 on FRDM-KL43Z board is PTE23/ADC0_SE7a. We had searched PTE23 and PTE29 pins on FRDM-KL43Z board with incorrect view thus we measured value at wrong pins.

Thanks for correcting us! Now we are getting correct values at both PTE23 and PTE29 pins.

Sorry for misunderstanding!

Thanks,

Vinayak Wadkar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Vinayak,

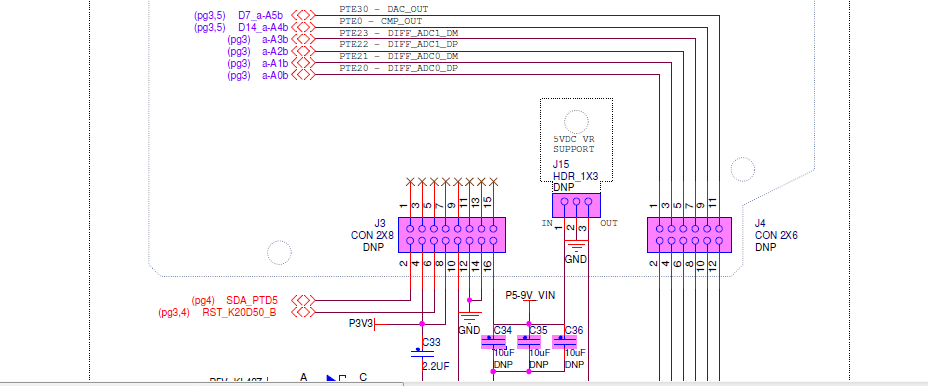

I have checked, the pin 7 of J4 on FRDM-KL43Z board is PTE23/ADC0_SE7a. I paste a screenshot, the PTE23 is the third line from right, pin 7 is the third line from right.

BR

Xiangjun rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Could you please recheck that PTE23/ADC0_SE7a is at pin 7 of J4 on FRDM-Kl43Z board ? I just verified PTE23/ADC0_SE7a is at pin 9 of J4 on FRDM-Kl43Z board and at pin7 of J4 on FRDM-Kl43Z board, there is ADC0_SE3 channel/PTE22.

Could you please retest for ADC0_SE7a pin(PTE23) and ADC0_SE4b pin(PTE29) and let us know your result ?

For ADC0_SE4b pin(PTE29), we are also setting MUX bit to 1 to select b channel.

Thanks,

Vinayak Wadkar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Vinayak,

Regarding your question, I have checked the FRDM-KL43Z board, are you sure that you get the correct J19? it seems that there are two J19 jumper from the top layer of the board. I suggest you check the bottom layer of the board, the bottom layer show the correct J19 jumper, pls close it.

Hope it can help you.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We are using correct J19 jumper of FRDM-KL43Z freedom board. We verified it by checking voltage on J19 jumpers point.

Could you please check for problem that we are facing in ADC value reading and let us know what exactly wrong?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for your reply!

We reviewed your code, which is similar to our code. As you tested your code for ADC0_SE0 pin(PTE20), we too tested our code for ADC0_SE0 pin(PTE20) and it worked fine. We got correct ADC result for ADC0_SE0 pin(PTE20).

Earlier we were testing ADC result for ADC0_SE7a pin(PTE23) and ADC0_SE4b pin(PTE29) and we we not getting exact values as discussed earlier in problem.

By the way were not using ADC0_SE7a and ADC0_SE4b pins in our actual project, but we chose these pins for testing just because they were free on FRDM-KL43Z freedom board.

Could you please tell exact reason for why ADC result was not proper for ADC0_SE7a and ADC0_SE4b ?This will help us in selecting ADC channels henceforth.

Thanks for your kind good support!

Thanks,

Vinayak Wadkar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Vinayak,

I just tested the ADC0_SE7b pin which is multiplexed with PTD6 or pin8 of J2 in FRDM-Kl43Z, if I set MUX of PORTD_PCR6 as 1, the test result is correct.

I copy the code here:

Hope it can help you.

BR

XiangJun Rong

#include "MKL43Z4.h"

void ADCInit(void);

static int i = 0;

unsigned short sample;

int main(void)

{

/* Write your code here */

ADCInit();

/* This for loop should be replaced. By default this loop allows a single stepping. */

for (;;) {

i++;

ADC0_CFG2|=0x10; //set channel b

ADC0_SC1A=0x07;

while(!(ADC0_SC1A&0x80)) {}

sample=ADC0_RA;

__asm("nop");

}

/* Never leave main */

return 0;

}

////////////////////////////////////////////////////////////////////////////////

// EOF

////////////////////////////////////////////////////////////////////////////////

void ADCInit(void)

{

//enable ADC gated clock

SIM_SCGC6|=0x8000000;

//set the ADC channel pin PTE20 and ADC channel ADC0_SE0

SIM_SCGC5|=0x2000;

PORTE_PCR20&=~(0x700);

//set PTD6 as ADC0_SE7B

SIM_SCGC5|=0x1000; //enable PORTD gated clock

PORTD_PCR6&=~(0x700);

PORTD_PCR6&=(0x100); //set MUX bits so that the pin PTD6 function as ADC_SE7b

//set ADC module

ADC0_CFG1 = 0x00000008; //Normal powered ADC

//Clock source selected as input bus clock with devide ratio of 1

//Short sample time

//10 bit single ended ADC operation

ADC0_SC2 = 0x00000000; //Select ADC trigger as software trigger

//Disable compare function

//Select ADC reference voltage source as defualt voltage reference source i.e. VREFH and //VREFL

ADC0_SC3 = 0x00000000; //SC3 register feature are not used thus keeping its value 0.

SystemCoreClockUpdate();

//ADC0_SC1n=0x00;

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

If I set MUX of PTD6 as 0, the ADC result is correct also.

Pls have a test.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I just tested PTE23/ADC0_SE7a with the following code, it is okay. The PTE23/ADC0_SE7a is pin 7 of J4 on FRDM-Kl43Z board. Pls have a try.

BR

Xiangjun Rong

#include "MKL43Z4.h"

void ADCInit(void);

static int i = 0;

unsigned short sample;

int main(void)

{

/* Write your code here */

ADCInit();

/* This for loop should be replaced. By default this loop allows a single stepping. */

for (;;) {

i++;

// ADC0_CFG2|=0x10; //set channel b

ADC0_CFG2&=~(0x10); //select channel a

ADC0_SC1A=0x07;

while(!(ADC0_SC1A&0x80)) {}

sample=ADC0_RA;

__asm("nop");

}

/* Never leave main */

return 0;

}

////////////////////////////////////////////////////////////////////////////////

// EOF

////////////////////////////////////////////////////////////////////////////////

void ADCInit(void)

{

//enable ADC gated clock

SIM_SCGC6|=0x8000000;

//set the ADC channel pin PTE20 and ADC channel ADC0_SE0

SIM_SCGC5|=0x2000;

// PORTE_PCR20&=~(0x700);

PORTE_PCR23&=~(0x700);

#if 0

//set PTD6 as ADC0_SE7B

SIM_SCGC5|=0x1000; //enable PORTD gated clock

PORTD_PCR6&=~(0x700);

// PORTD_PCR6&=(0x100); //set MUX bits so that the pin PTD6 function as ADC_SE7b

#endif

//set ADC module

ADC0_CFG1 = 0x00000008; //Normal powered ADC

//Clock source selected as input bus clock with devide ratio of 1

//Short sample time

//10 bit single ended ADC operation

ADC0_SC2 = 0x00000000; //Select ADC trigger as software trigger

//Disable compare function

//Select ADC reference voltage source as defualt voltage reference source i.e. VREFH and //VREFL

ADC0_SC3 = 0x00000000; //SC3 register feature are not used thus keeping its value 0.

SystemCoreClockUpdate();

//ADC0_SC1n=0x00;

}