- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Flexbus SRAM SIZE

Flexbus SRAM SIZE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Flexbus SRAM SIZE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

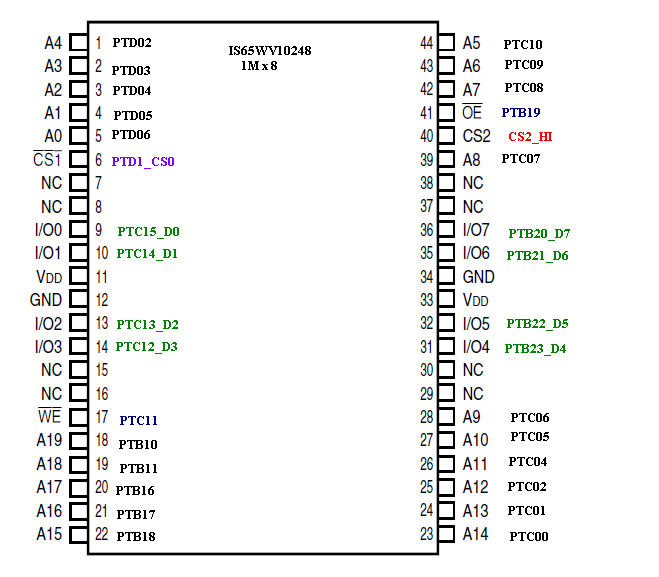

my teste Flexbus + SRAM ( IS62WV10248DALL ) 1MBx8

CPU = K22FX512 , Clock = 120, core,bus,flexbus =60

Problems: 0x0000 0000 to 0x0000 7FFF ( READ AND WRITE ) = OK

> 0x0000 7FFF , not ( read and write ) , return to 0x00000000 page0.

Connection hw:

void setup_fb_sram_ (void){

#define SRAM_START_ADDRESS (*(volatile uint32_t*)(0x60000000))

FB_CSAR0 = (uint32_t)&SRAM_START_ADDRESS;

FB_CSCR0 = FB_CSCR_PS(1) // 8-bit port

| FB_CSCR_AA_MASK // auto-acknowledge

// | FB_CSCR_ASET(0x1) // add assert chip select on second clock edge after address is asserted

| FB_CSCR_WS(0x2); // 2 wait states

FB_CSMR0 = FB_CSMR_BAM(0x00FF) // 1MB

| FB_CSMR_V_MASK //Enable cs valid signal

SIM_SCGC5 |= SIM_SCGC5_PORTB_MASK; // Enable Clock to PORTB

SIM_SCGC5 |= SIM_SCGC5_PORTC_MASK; // Enable Clock to PORTC

SIM_SCGC5 |= SIM_SCGC5_PORTD_MASK; // Enable Clock to PORTD

PORTB_PCR11 = PORT_PCR_MUX(5); // fb_ad[18]

PORTB_PCR16 = PORT_PCR_MUX(5); // fb_ad[17]

PORTB_PCR17 = PORT_PCR_MUX(5); // fb_ad[16]

PORTB_PCR18 = PORT_PCR_MUX(5); // fb_ad[15]

PORTC_PCR0 = PORT_PCR_MUX(5); // fb_ad[14]

PORTC_PCR1 = PORT_PCR_MUX(5); // fb_ad[13]

PORTC_PCR2 = PORT_PCR_MUX(5); // fb_ad[12]

PORTC_PCR4 = PORT_PCR_MUX(5); // fb_ad[11]

PORTC_PCR5 = PORT_PCR_MUX(5); // fb_ad[10]

PORTC_PCR6 = PORT_PCR_MUX(5); // fb_ad[9]

PORTC_PCR7 = PORT_PCR_MUX(5); // fb_ad[8]

PORTC_PCR8 = PORT_PCR_MUX(5); // fb_ad[7]

PORTC_PCR9 = PORT_PCR_MUX(5); // fb_ad[6]

PORTC_PCR10 = PORT_PCR_MUX(5); // fb_ad[5]

PORTD_PCR2 = PORT_PCR_MUX(5); // fb_ad[4]

PORTD_PCR3 = PORT_PCR_MUX(5); // fb_ad[3]

PORTD_PCR4 = PORT_PCR_MUX(5); // fb_ad[2]

PORTD_PCR5 = PORT_PCR_MUX(5); // fb_ad[1]

PORTD_PCR6 = PORT_PCR_MUX(5); // fb_ad[0]

PORTB_PCR20 = PORT_PCR_MUX(5); // fb_ad[31] used as d[7]

PORTB_PCR21 = PORT_PCR_MUX(5); // fb_ad[30] used as d[6]

PORTB_PCR22 = PORT_PCR_MUX(5); // fb_ad[29] used as d[5]

PORTB_PCR23 = PORT_PCR_MUX(5); // fb_ad[28] used as d[4]

PORTC_PCR12 = PORT_PCR_MUX(5); // fb_ad[27] used as d[3]

PORTC_PCR13 = PORT_PCR_MUX(5); // fb_ad[26] used as d[2]

PORTC_PCR14 = PORT_PCR_MUX(5); // fb_ad[25] used as d[1]

PORTC_PCR15 = PORT_PCR_MUX(5); // fb_ad[24] used as d[0]

PORTB_PCR19 = PORT_PCR_MUX(5); // fb_oe_b

PORTC_PCR11 = PORT_PCR_MUX(5); // fb_rw_b

PORTD_PCR1 = PORT_PCR_MUX(5); // fb_cs0_b

}

//---------------------------------------SRAM WRITE

void sram_write_byte ( uint32_t adress , byte valor ){

*(volatile uint32_t*)( &SRAM_START_ADDRESS + adress ) = valor;

}

//---------------------------------------SRAM READ

byte sram_read_byte(uint32_t adress ){

return( *(volatile uint32_t*)( &SRAM_START_ADDRESS + adress ));

}

//------------------------------------

thanks;

Carlos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

can you share your whole Flexbus configuration?

Regards,

Carlos

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

The complete configuration is the same, alas this whole code.

I can read and write (0x0000 to 0x7FFF),

higher addresses can not be reached, eventually returning to BASE_SRAM.

one thing I noticed,arises proper value in FB_CSMR_BAM (0x000F (1MB) ) = ERROR FLEXBUSS. not init cpu.

thanks,

Carlos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

You must use FB_CSMR0 = FB_CSMR_BAM(0xF);

Please check if the register value is set correctly. Otherwise check hardware connection, most likely this is the problem.

Regards,

Carlos