- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- FlexIO SPI Configuration without Chip Select and SDI

FlexIO SPI Configuration without Chip Select and SDI

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

FlexIO SPI Configuration without Chip Select and SDI

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

I am using MKE17Z256 micro-controller, and I have to communicate with an another chip over SPI, but without SDI and Chip Select Pin, which means I want to use FlexIO in SPI but without Chip Select and Serial Data Input. I took the FlexIO SPI example from the SDK, and removed the LSPI Slave related code to keep things simple, but I am facing a problem that data doesn't seems transmitted properly (my observation is data transmitted is correct, but there is some issue with the Clock line, probably Chip Select or SDI are not disabled and hence this is happening)

#include "fsl_debug_console.h"

#include "fsl_lpspi.h"

#include "fsl_flexio_spi.h"

#include "pin_mux.h"

#include "board.h"

#include "fsl_common.h"

/*******************************************************************************

* Definitions

******************************************************************************/

/*Master related*/

#define TRANSFER_SIZE 5U /*! Transfer dataSize */

#define TRANSFER_BAUDRATE 500000U /*! Transfer baudrate - 500k */

#define MASTER_FLEXIO_SPI_BASEADDR FLEXIO

#define FLEXIO_SPI_SOUT_PIN 4U

// #define FLEXIO_SPI_SIN_PIN 7U

#define FLEXIO_SPI_CLK_PIN 0U

// #define FLEXIO_SPI_PCS_PIN 6U

#define MASTER_FLEXIO_SPI_IRQ FLEXIO_IRQn

#define MASTER_FLEXIO_SPI_CLOCK_NAME kCLOCK_Flexio0

#define MASTER_FLEXIO_SPI_CLOCK_SOURCE kCLOCK_IpSrcFircAsync

#define MASTER_FLEXIO_SPI_CLOCK_FREQUENCY CLOCK_GetIpFreq(MASTER_FLEXIO_SPI_CLOCK_NAME)

// Function Prototypes

void FLEXIO_SPI_MasterUserCallback(FLEXIO_SPI_Type *base,

flexio_spi_master_handle_t *handle,

status_t status,

void *userData);

// Variables

uint8_t masterTxData[TRANSFER_SIZE] = {0U};

FLEXIO_SPI_Type spiDev;

flexio_spi_master_handle_t g_m_handle;

volatile bool isMasterTransferCompleted = false;

// Function Definitions

void FLEXIO_SPI_MasterUserCallback(FLEXIO_SPI_Type *base,

flexio_spi_master_handle_t *handle,

status_t status,

void *userData)

{

if (status == kStatus_Success)

{

__NOP();

}

isMasterTransferCompleted = true;

}

// Main Program

int main(void)

{

BOARD_InitBootPins();

BOARD_InitBootClocks();

BOARD_InitDebugConsole();

/*Set clock source for LPSPI and FlexIO*/

CLOCK_SetIpSrc(MASTER_FLEXIO_SPI_CLOCK_NAME, MASTER_FLEXIO_SPI_CLOCK_SOURCE);

uint32_t i;

flexio_spi_master_config_t masterConfig;

flexio_spi_transfer_t masterXfer;

/* Master config */

FLEXIO_SPI_MasterGetDefaultConfig(&masterConfig);

masterConfig.baudRate_Bps = TRANSFER_BAUDRATE;

spiDev.flexioBase = MASTER_FLEXIO_SPI_BASEADDR;

spiDev.SDOPinIndex = FLEXIO_SPI_SOUT_PIN;

// spiDev.SDIPinIndex = FLEXIO_SPI_SIN_PIN;

spiDev.SCKPinIndex = FLEXIO_SPI_CLK_PIN;

// spiDev.CSnPinIndex = FLEXIO_SPI_PCS_PIN;

spiDev.shifterIndex[0] = 0U;

spiDev.shifterIndex[1] = 1U;

spiDev.timerIndex[0] = 0U;

spiDev.timerIndex[1] = 1U;

FLEXIO_SPI_MasterInit(&spiDev, &masterConfig, MASTER_FLEXIO_SPI_CLOCK_FREQUENCY);

/* Set up the transfer data */

for (i = 0U; i < TRANSFER_SIZE; i++)

{

masterTxData[i] = i % 256U;

}

/* Set up master transfer */

FLEXIO_SPI_MasterTransferCreateHandle(&spiDev, &g_m_handle, FLEXIO_SPI_MasterUserCallback, NULL);

/*Start master transfer*/

masterXfer.txData = masterTxData;

masterXfer.rxData = NULL;

masterXfer.dataSize = TRANSFER_SIZE;

masterXfer.flags = kFLEXIO_SPI_8bitMsb;

isMasterTransferCompleted = false;

FLEXIO_SPI_MasterTransferNonBlocking(&spiDev, &g_m_handle, &masterXfer);

/* Wait slave received all data. */

while (!(isMasterTransferCompleted))

{

}

FLEXIO_SPI_MasterDeinit(&spiDev);

while (1);

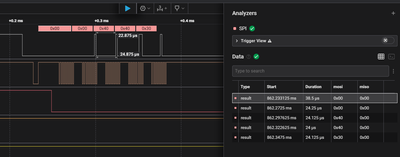

}I transmitted 0x00, 0x01, 0x02, 0x03, 0x04, but as per Logic Analyzer I am getting 0x00, 0x00, 0x40, 0x40, 0x40, 0x30

If u see the logic analyzer window it seems that data is fine, but clock is the problem and due to which data is not decoded properly.

Since I used FlexIO-4 as SDO and FlexIO-0 as Clock, and as I did not configured Chip Select and SDI, so they will also becomes "0" means FlexIO-0 pin, and somehow this is causing the problem.

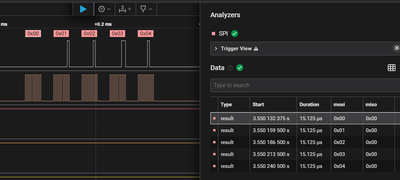

So, to solve this I did a workaround, I assigned SDI and Chip Select pin to some other FlexIO Pin i.e. 1 in this case. and then enabled these pins in code.

The change from the above code is as below.

#define FLEXIO_SPI_SOUT_PIN 4U

#define FLEXIO_SPI_CLK_PIN 0U

#define FLEXIO_SPI_SIN_PIN 1U // dummy

#define FLEXIO_SPI_PCS_PIN 1U // dummy

// and then below changes

spiDev.flexioBase = MASTER_FLEXIO_SPI_BASEADDR;

spiDev.SDOPinIndex = FLEXIO_SPI_SOUT_PIN;

spiDev.SDIPinIndex = FLEXIO_SPI_SIN_PIN; // enabled with dummy FlexIO pin

spiDev.SCKPinIndex = FLEXIO_SPI_CLK_PIN;

spiDev.CSnPinIndex = FLEXIO_SPI_PCS_PIN; // enabled with dummy FlexIO pin

spiDev.shifterIndex[0] = 0U;

spiDev.shifterIndex[1] = 1U;

spiDev.timerIndex[0] = 0U;

spiDev.timerIndex[1] = 1U;And after these changes it started working, as can be seen below.

The problem is I don't have spare pins to be used like this, I assume there might be some other way also, but I am not able to understand properly how to achieve this using shifters and timers configuration.

I tried by removing these two lines but doesn't work.

spiDev.shifterIndex[1] = 1U;

spiDev.timerIndex[1] = 1U;I also tried setting shifter and timer configuration to disable the pin configuration for Chip Select, but nothing works "timerConfig.pinConfig = kFLEXIO_PinConfigOutputDisabled;"

Can someone please suggest, what is the correct way to setup this?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any suggestions ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The configuration we share on the Reference Manual for configuring FlexIO as SPI is made accordingly for the specification of SPI.

Also, because of synchronization delays, the setup time for the serial input data is 1.5 FLEXIO clock cycles. This means the maximum baud rate is divide by 4 of the FLEXIO clock frequency.

There may be other configurations for FlexIO that could fulfill your application; however, this configuration may be done on the customer's end.

Best Regards,

Pablo