- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- FTM standalone timer

FTM standalone timer

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

FTM standalone timer

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I need an exampe for FTM as a standalone timer.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Vignesh,

try this part of code:

void FTM0_init()

{

FTM0_SC = 0x00;

FTM0_CNTIN = FTM_CNTIN_INIT(0);

FTM0_MOD = FTM_MOD_MOD("your value"); //your value should be smaller than 65535!

FTM0_SC = FTM_SC_CLKS(0x01) | FTM_SC_PS(0);

}

If you need more support, please give us more input :smileywink:

Pascal

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pascal,

I want to understand about clocks I. FTM timer and how the clock affects the timer.Can you provide me a calculation for the each FTM count based on clocks?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

especially for the FTM I calculated the specific modv and prescaler values for my bachelor thesis like this:

NOTE: period_us is the suggested timer period in us!

CORE_PERIOD_NS is the period time of your system clock in ns!

/* This routine calculates the modv value in combination with

* a suitable prescaler. If there is no suitable prescaler =>

* the value is too tall and an error code will be set

* Calculation: Register Value = period_us / CORE_PERIOD

* us/ns = 1*10^-3 => pow(10,3) */

modv = (period_us/CORE_PERIOD_NS)*pow(10,3);

/* In the FTM0_MOD register are only 16bits available => 65535 */

while((period_us/CORE_PERIOD_NS)*pow(10,3)>65535)

{

/* The value 7 is the tallest available prescaler (see datasheet) */

if(prescaler>7)

{

program_error(PROGRAM_ERROR_ftm);

break;

}

prescaler++;

/* Every prescaler multiplies the time with factor 2 => time value /= 2 */

modv /= 2;

/* modv /= 2 accords with period_us (see the calculation in the while loop) */

period_us /= 2;

}

So your timer period depends on your selected clock, your clock frequency the modv value and your selected prescaler!

Cheers,

Pascal

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pascal,

I want to know about the core period?How do I find it out?I am using KEA-128

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

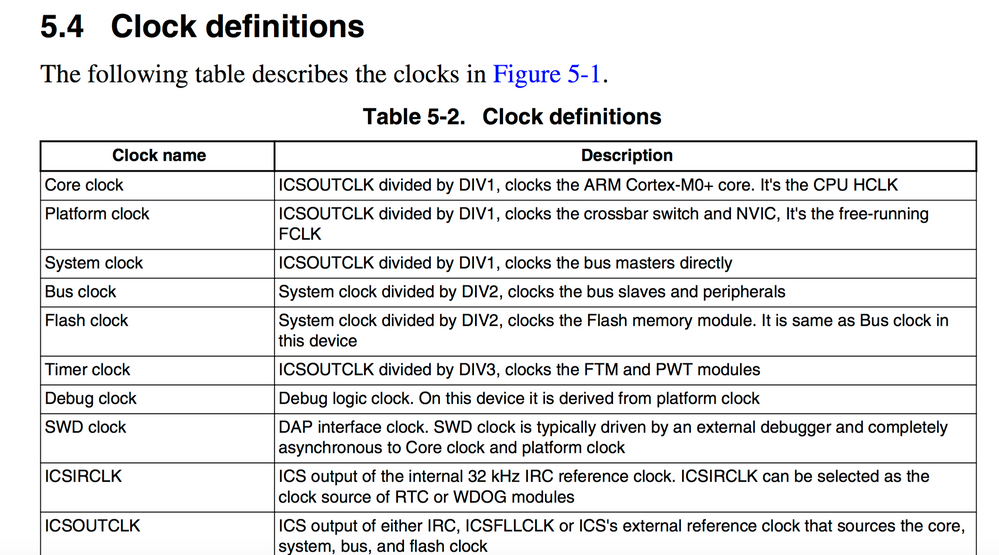

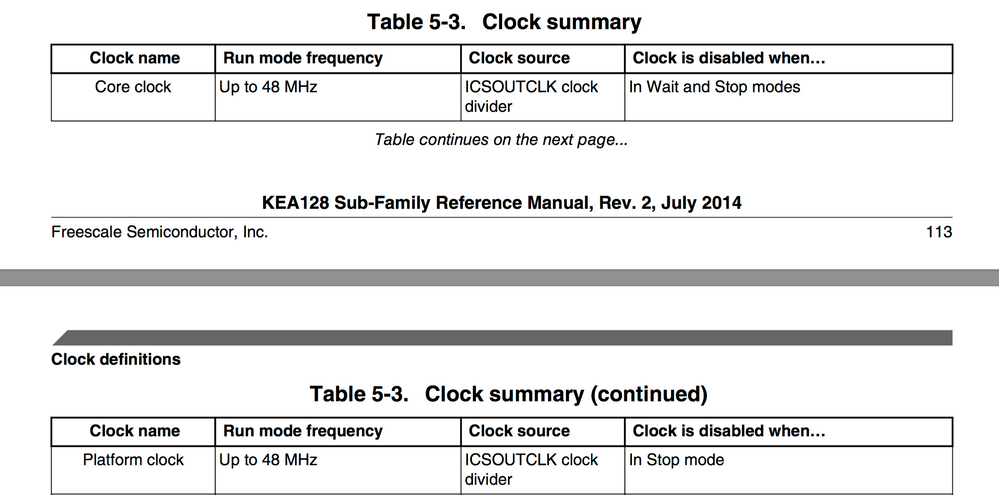

Have a look:

First step of starting an embedded system is to initialize your clocks!

Cheers,

Pascal

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, all,

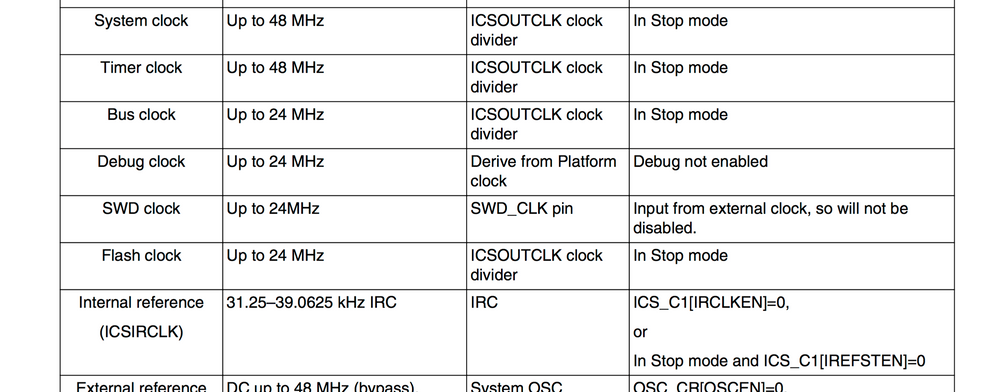

Regarding the FTM driving clock, it is dependent on the FTM clock source and prescaler, in other words, the FTM driving clock frequency equals to (FTM clock source frequency)/Prescaler.

The CLKS bits in FTM_SC register determines the FTM clock source for KEA128 chip:

CLKS bits clock source

00 FTM disabled

01 system clock source

10 Fixed frequency clock

11 External clock source

Pls refer to Figure 5-3. FTM and PWT clock generation in the KEA128RM.pdf for the detailed FTM clock source.

When the CLKS=01, the system clock source is selected, in the condition, the ICSOUTCLK clock source divided by DIV3 is used as FTM clock source, DIV3 bits is specified in SIM_CLKDIV. Pls refer to the Figure 5-1. Clocking diagram in KEA128RM.pdf.

when the CLKS=10, the ICSFFCLK clcok source is selected as FTM clock source, ICSFFCLK clock source is 37.5KHz IRC or (external OSC)/RDIV, pls refer to Figure 5-1. Clocking diagram.

when the CLKS=11, the FTM clcok source are from TCLK0/TCLK1/TCLK2 pins, SIM_PINSEL0[FTM0CLKPS] select the clock source pins from the three pins. Note TCLK0/TCLK1/TCLK2 are Kea128 external signal pads, for example:

This is the pin assignment of TCLK0 pin.

79(79 LQFP) 63(63 LQFP) PTA5, RESET_b, PTA5 KBI0_P5, IRQ, TCLK0, RESET_b

In otherwords, you can connect the external clock source to the TCLK0 pin, the FTM driving clock frequency will be (TCLK0 Pin clock frequency)/Prescaler, the prescaler is defined in the FTM_SC register.

Note you should enable the FTM gate clock by setting the corresponding bit in SIM_SCGC register when you use CLKS=01 setting..

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, all,

Pls refer to an5142 for the FTM features and corresponding code, but you have to add the code to select the FTM clock source based on KEA128RM.

Pls go to the website and download "features of FlexTimer Module"

K40_100 |Kinetis K40 100 MHz MCUs|NXP

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I need to run the clock of my KEA-128 at 24 Mhz.I am finding

difficulty in setting the ICS_C1 register in it.Can you provide me any

example for it?

On Sat, Jan 16, 2016 at 1:03 AM, pascalschröer <

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Maybe it's more easier to say:

Your modv value (modification value) is calculated like this:

modv = period_time / system_clock_period

If your modv value is too large (<65535), you can use a prescaler. Every prescaler level divides your modv value by 2.

Cheers,

Pascal

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Can you give me more clarity on period time and system clock