- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: FTM settings on KEA

FTM settings on KEA

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

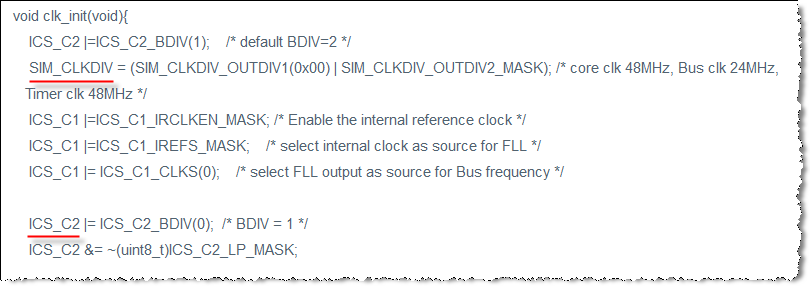

Hello all,

i am trying to setup the FTM modul to generate 50us interrupt. The FTM works with 48MHz and i select a prescaler of 64. that means the timer has a period of 1.3333us. So to have 50us i shoul set the channel counter (FTMx_CxV) to 37. But what i measure is an 25us interrupt?? it looks like the FTM clock source is 24MHz and not 48MHz! here ist hte Clock setting and the FTM init code:

void clk_init(void){

ICS_C2 |=ICS_C2_BDIV(1); /* default BDIV=2 */

SIM_CLKDIV = (SIM_CLKDIV_OUTDIV1(0x00) | SIM_CLKDIV_OUTDIV2_MASK); /* core clk 48MHz, Bus clk 24MHz, Timer clk 48MHz */

ICS_C1 |=ICS_C1_IRCLKEN_MASK; /* Enable the internal reference clock */

ICS_C1 |=ICS_C1_IREFS_MASK; /* select internal clock as source for FLL */

ICS_C1 |= ICS_C1_CLKS(0); /* select FLL output as source for Bus frequency */

ICS_C2 |= ICS_C2_BDIV(0); /* BDIV = 1 */

ICS_C2 &= ~(uint8_t)ICS_C2_LP_MASK;

OSC_CR = 0x00U; /* disable OSC Module */

while((ICS_S & ICS_S_IREFST_MASK) != 0x10U) { /* Check that the source of the FLL reference clock is the internal reference clock. */

}

while((ICS_S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */

}

}

void FTM2_Init(void){

SIM_SCGC |= SIM_SCGC_FTM2_MASK; /* enable clock for FTM0 _Freescale_*/

FTM2_SC |= FTM_SC_PS(6); /* select prescaler -> 64 _Freescale: Value adjusted_*/

FTM2_C0SC |= FTM_CnSC_CHIE_MASK; /* enable channel 0 interrupt _Freescale_*/

FTM2_C0SC |= FTM_CnSC_MSA_MASK; /* channel works in output compare mode _Freescale_*/

FTM2_C0V = 37; /* every 50µs */

FTM2_SC |= FTM_SC_CLKS(1); /* FTM0 uses system clock _Freescale_*/

}

what could be the problem? if i assume that the Timer clk is 24MHz every thing works fine.

thank you for helping.

Hani

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hani,

Please refer the code shown below:

/* ICS_C2: BDIV=0,LP=0 */

ICS_C2 &= (uint8_t)~(uint8_t)((ICS_C2_BDIV(0x07) | ICS_C2_LP_MASK));

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hani,

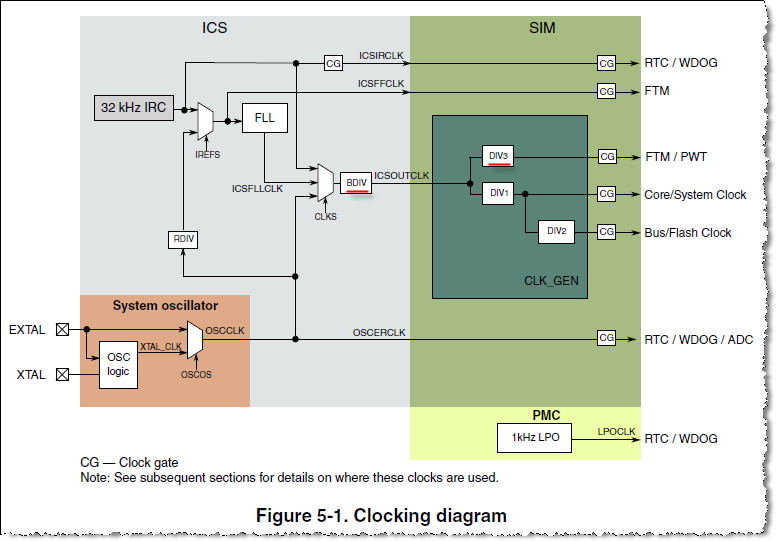

Since you are using KEA ZN8, Timer clock(ICSOUTCLK divided by DIV3) clocks the FTM and PWT modules.

You need to check whether the SIM_CLKDIV[OUTDIV3] and ICS_C2[BDIV] are correct configured.

I didn't see the SIM_CLKDIV_OUTDIV3 in clk_init().

You can't set the value of BDIV like that. Since the BDIV is default to 0x01, it will still equal to 0x01.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Robin,

Thank you for answer.

for OUT_DIV3 i set it many times to 0, but it dose not help.

for the BDIV i set it in the code to be zero, i.e. ICSOUTCLK divided by one. (ICS_C2 |= ICS_C2_BDIV(0)).

My configuration:

1. FLL out = 48MHz

2. BDIV = 1 default divide by 2

3. ICSOUTCLK = 24MHz

4. DIV1=0 (divide by 1)

5. DIV2=1 (divide by 2)

6. DIV3=0 (divide by1)

7. BDIV = 0 (divide by 1) --> ICSOUTCLK = 48MHz

-- FTM/PWT clk = 48MHz

-- Core clk = 48MHz

-- Bus clk = 24MHz

but as i told Mark in the previous Post, i donot understand why we should enable the bus clk for the FTM in the FTM init code??! (SIM_SCGC |= SIM_SCGC_FTM2_MASK; /* enable bus clock for FTM0 _Freescale_*/)

if i remove this line the timer did not started at all!

Regards

Hani

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hani,

Please refer the code shown below:

/* ICS_C2: BDIV=0,LP=0 */

ICS_C2 &= (uint8_t)~(uint8_t)((ICS_C2_BDIV(0x07) | ICS_C2_LP_MASK));

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Robin,

Thank you very much. You are right, it is an OR operation, so the 0x01 still remains. It works fine now.

Best Regards,

Hani

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hani

The timer module in the Kinetis KEA parts is clocked from the BUS clock, which you have set to 24MHz.

If you are getting values for a 24MHz clock it sounds as though all is normal.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hallo Mark,

thank you.

in the reference manual as you can see in Robin post, you can configure the FTM/PWT to have 48MHz! but what this line means in the FTM_init:

SIM_SCGC |= SIM_SCGC_FTM2_MASK; /* enable clock for FTM0 _Freescale_*/

it enables the bus clock for the the FTM modul?! i took this code from Freescale getting started document.

Regards

Hani

![SIM_CLKDIV[OUTDIV3].png SIM_CLKDIV[OUTDIV3].png](/t5/image/serverpage/image-id/15401iD889531C02270BDA/image-size/large?v=v2&px=999)

![ICS_C2[BDIV].png ICS_C2[BDIV].png](/t5/image/serverpage/image-id/15490iEE24CBA3D72EEDA9/image-size/large?v=v2&px=999)