- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: FLL and PLL Disabled in BLPI mode

FLL and PLL Disabled in BLPI mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

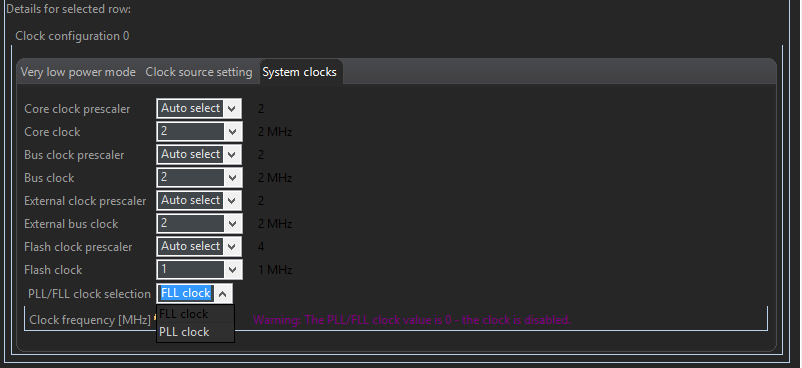

It's to my understanding that in the Bypassed Low Power Internal, the FLL and PLL are disabled. However, when I set the clock configuration I get a warning:

| Description | Resource | Path | Location | Type |

| Warning: The PLL/FLL clock value is 0 - the clock is disabled. (Clock frequency [MHz]) | Cpu/Clock frequency [MHz] | Processor Expert Problem |

So, what's the actual problem with disabling both? Why am I getting this warning? BLPI mode is the only mode that allows me to use Very Low Power Mode, which is the purpose in using that as opposed to other modes. This is the only clock configuration.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dane

I suspect that the warning that you are getting can be ignored since, as you know, BLPI is the same as FBI as far as the processor core is concerned.

However beware that it may be possible for perpherals to (optionally) use the FLL or PLL outputs (MCGPPLCLK/MCGFLLCLK) in FBI and maybe the warning is due to that (?).

There are some practical details at http://www.utasker.com/kinetis/MCG.html

In the case of VLPS mode I don't think that you need to worry about whether you are in BLPI or FBI since the PLL and FLL will automatically be stopped anyway.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dane

I suspect that the warning that you are getting can be ignored since, as you know, BLPI is the same as FBI as far as the processor core is concerned.

However beware that it may be possible for perpherals to (optionally) use the FLL or PLL outputs (MCGPPLCLK/MCGFLLCLK) in FBI and maybe the warning is due to that (?).

There are some practical details at http://www.utasker.com/kinetis/MCG.html

In the case of VLPS mode I don't think that you need to worry about whether you are in BLPI or FBI since the PLL and FLL will automatically be stopped anyway.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks, I guess that makes sense why the warning is there, but not necessarily why won't didn't disappear. I just check all my components and they aren't using the FLL (or PLL) clocks. I think its just PE forcing me to chose to use the PLL or FLL, and isn't smart enough to handle no PLL or FLL.