ADC sampling rate

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I tried to follow up on a old question "https://community.nxp.com/thread/437073", but I didn't get any answers, so now I am raising my own thread.

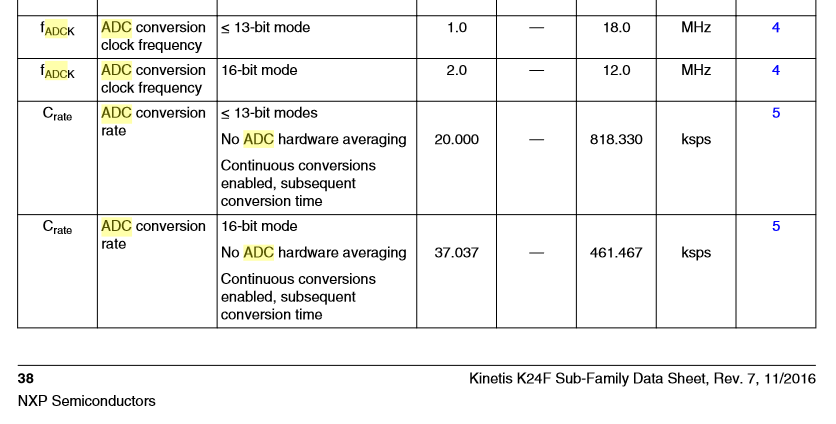

Based on the K24 Kinetis datasheet:

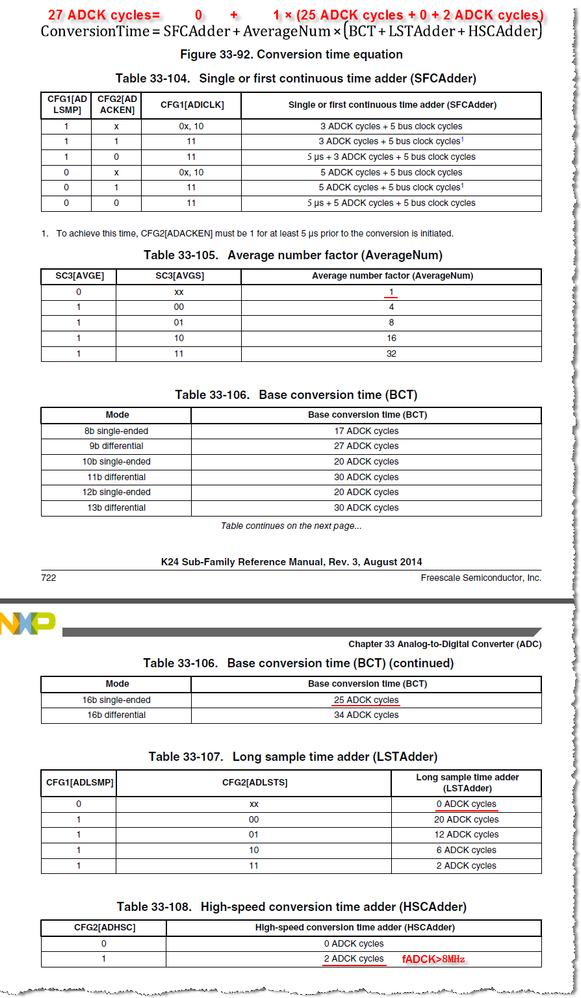

I do not understand, how a sample rate of 461.467 ksps is reachable with a ADC clock limited to 12 MHz. Don't you need 34 adc_clks + 5 adc_clks + 5 bus_clks = 39 adc_clks + 5 bus_clks?

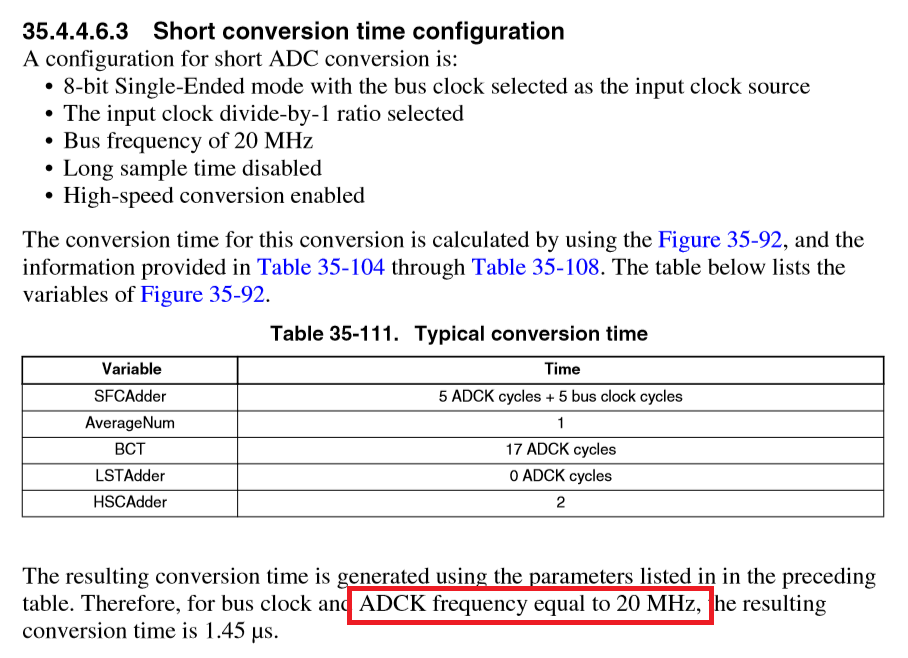

Also, I do see sources talking about high clock frequency than 18 MHz (<= 13 bit mode). E.g. in this example for the same K24 Kinetis datasheet:

Please, would someone tell me how the 461.467 ksps sample rate is reachable and at which ADC clock?

Thanks, Ulrik

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ulrik,

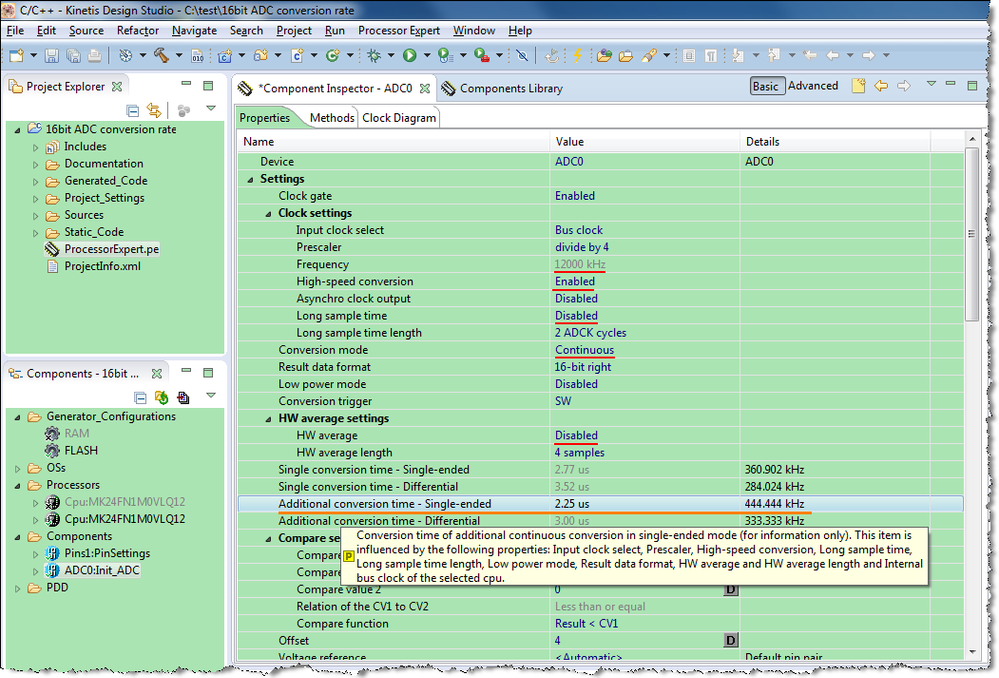

With the ADC clock=12MHz, I think it should be 12MHz / 27 = 444.444 ksps

This meet the result in Processor Expert:

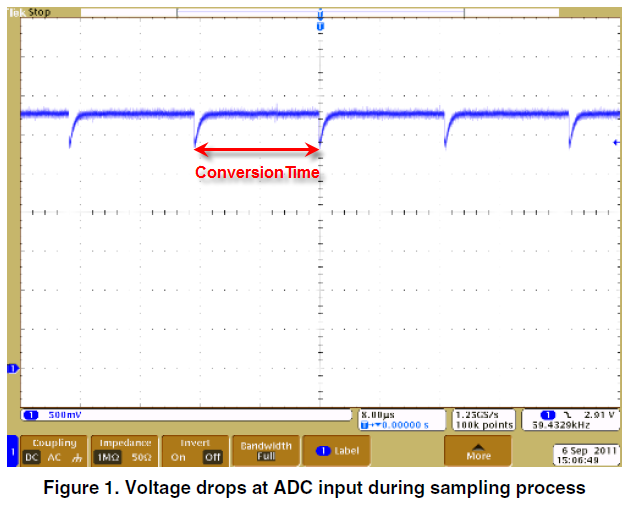

Refer to the phenomenon descripted in"Figure 1. Voltage drops at ADC input during sampling process" of AN4373.

I think you can observe the waveform of ADC conversion rate on your ADC input pin.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------