- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- ADC sampling

ADC sampling

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC sampling

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everybody,

I'am using the ADC16 on the K64 and here's my config:

Enable the ADC0 Clock

SIM->SCGC6 |= SIM_SCGC6_ADC0_MASK;

CFG1 CONF

ADC0->CFG1 = (0 << 7) | /* Normal power configuration.*/

(0 << 5) | /* The divide ratio is 1 and the clock rate is input clock. */

(0 << 4) | /* Select short sample time*/

(3 << 2) | /* Select 16-bit conversion*/

(0 << 0); /* Input clock is (Bus clock)*/

CFG2 CONF

ADC0->CFG2 = (0 << 4) | /* ADxxa channels are selected*/

(0 << 3) | /* Async clock output disabled*/

(1 << 2) | /*High-speed conversion sequence */

(3 << 0); /* 2 extra ADCK cycles; 6 ADCK cycles total sample time. */

SC1 CONF

ADC0->SC1[0] = (1 << 6) | /* Conversion complete interrupt enabled */

(1 << 5) | /* DIFF conversions and input ch are selected */

(1 << 0); /* Select DAD1 as input*/

SC2 CONF

ADC0->SC2 = (0 << 6) | /* Software trigger selected*/

(0 << 5) | /* Compare function disabled*/

(0 << 4) | /* Compare configures less than threshold */

(0 << 3) | /* Range function disabled*/

(0 << 2) | /* DMA is disabled*/

(0 << 0); /* Default voltage reference*/

SC3 CONF

ADC0->SC3 |= (0 << 2) | /* Hardware average function disabled */

1)How to set the adc on maximum sampling rate ?

2) How to determine the value of the ADC maximum sampling rate with a custom configuration?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ahmed hrabi,

1)How to set the adc on maximum sampling rate ?

Do you want to set the sample time or conversation rate?

Sample time, you can find it from the K64 reference manual:

To select which sample time, it determined by your hardware, more details, please read this application note:

http://cache.nxp.com/files/microcontrollers/doc/app_note/AN4373.pdf

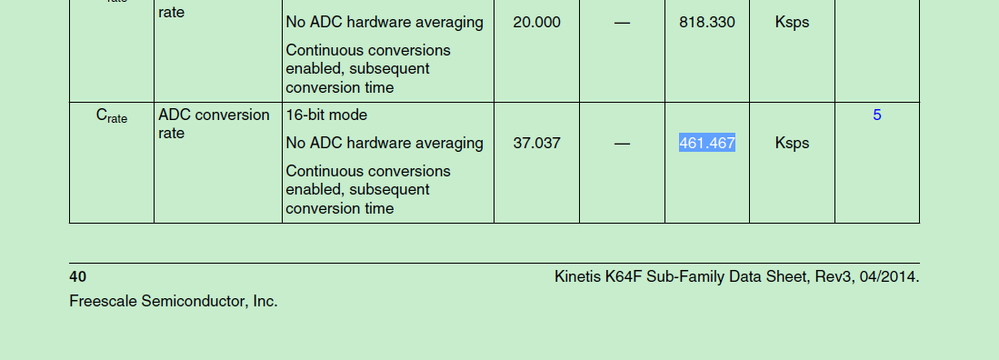

About the max conversation time for 16 bit, you can find it from the K64 datasheet:

2) How to determine the value of the ADC maximum sampling rate with a custom configuration?

I think you want to know the adc conversation rate, not the sampling rate.

If you know how to calculate the conversation rate, then it is easy to know the conversation rate from the customer configuration.

Please read the k64 reference manual, chapter 35.4.4.5 Sample time and total conversion time.

Just checking the customer's register configuration, then according to the above formula and calculate it.

Please calculate it by yourself at first.

If you still have question, please contact me!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes Kerry, would you please do the calculation for me. I am in the same situation. I don't get it. What you did not include in the tables above, is the fact, that the K64 has an ADC clock limit of 18 MHz (and 12 MHz in 16 bit mode). Now, will you please prove to me (and everybody else), how 16 bit resolution is reachable at 461 ksps?

I think NXP tries to hide the true convertion rates, and that the rates given in the datasheet is only for 8 bit resolution. Please prove that I am wrong. You will break my heart, if you say that the convertion rate is limited to 12 MHz / (34+5+5) clks = 272 ksps for 16 bit resolution and 18 MHz / (30+5+5) = 450 ksps in 13 bit resolution (differential). Here assuming the bus clock equals the adc clock - it does not really matter that much.

Best regards Ulrik

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And let me also add this. In the reference manual for K24 is an example where the ADC clock becomes 20 MHz, but which Kinetis chips can run at 20 MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content