- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: ADC Trigger Spacing

ADC Trigger Spacing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC Trigger Spacing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using a MKE18F16 MCU. I was having issues while using two ADCs simultaneously (ADC0 and ADC2). The issue was that ADC2 was performing significantly worse than ADC0. The same AutoCalibration mechanisms for both ADCs, and each ADC had its own unique calibration stored in NVM to be used out of reset. However, every time the device was reset, ADC2 would give different results that were not accurate at all. ADC0 sometimes would randomly give different results, but not to the extent that ADC2 was showing.

Since then, this error that was being observed with the two ADCs has gone down significantly. The issue was determined to be that both ADC0 and ADC2 were interfering with each other, because they were being triggered at the same time. ADC0 and ADC2 would both trigger at a 50% duty cycle, and since ADC0 was set to be triggered first, it is believed that this is why ADC0 performed better then ADC2. Changing the operation to give some space between ADC triggers fixed the issue.

Now the question is why? Why does having them trigger at the same time cause issues? Why does spacing them apart help? Is there any recommendation on how much time should be allocated between triggers?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

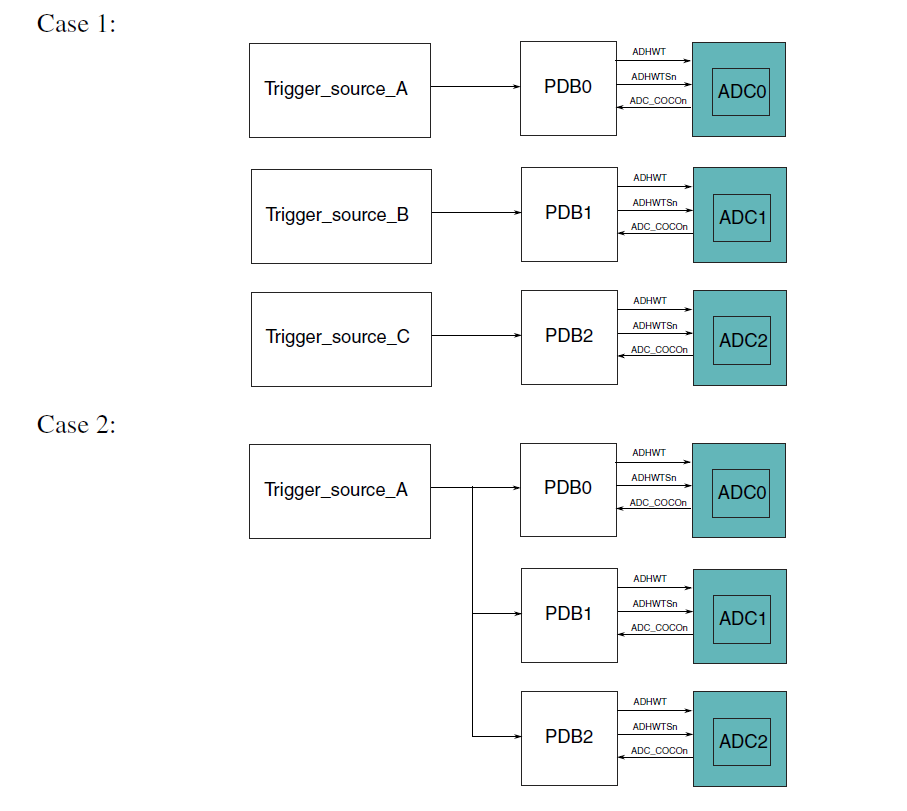

Originally, the configuration was set up to represent case 2. Changing it to resemble case 1 fixed the issue that I had.

Is there any reference on how much spacing I should have between ADC triggers?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sean,

The following application note, describes how to design the system timing.It states that it depends on how the peripheral resources are utilized and how the MCU performance is allocated. So there is not a minimum or maximum specified, but i believe this explains what are the considerations to be made.

In addition, this next application note also describes a similiar section. In section 2.2 you will find Timing of PDB. This is for the KE16Z, so please use it as a reference only.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the app notes. I looked through them and didn't really find what I was looking for.

From everything that I have read, using two ADC modules simultaneously should not effect ADC results. However, it seems that they do if you trigger them too close to each other.

I want to make the point that I am currently using FTM to trigger a DMA request to write to ADCx->SC1[0] every 4us to trigger a conversion.

Originally the set up was a single FTM channel would trigger a single DMA request to write to ADC0->SC1[0], then the DADDR would update to the ADC2->SC1[0]. Since then, I set up a new FTM channel and DMA channel that would operate specifically with ADC2. So now I have an FTM channel that triggers a DMA channel to write to ADC0->SC1[0], and an FTM channel that triggers a separate DMA channel to write to ADC2->SC1[0]. I have found that separating the FTM CnV for the two channels by about 2.8us gives me the best results. The question is why 2.8us, and why did I have to separate them in the first place?

There were also two separate DMA channels that will be triggered when conversions are completed. One DMA channel triggered on ADC0 COCO, and one DMA channel on ADC2 COCO.

I only bring this up because everything I read says that ADCs running in parallel should not interfere with each other. So that brings the question about whether it has to do more with my set up then the time between ADC triggers. Could DMA channels be taking priority over others, and that is somehow effecting the results of ADC2?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sean,

Hope you are doing well.

Could you please specify how you are triggering the ADC modules.

The issue was determined to be that both ADC0 and ADC2 were interfering with each other, because they were being triggered at the same time. ADC0 and ADC2 would both trigger at a 50% duty cycle, and since ADC0 was set to be triggered first, it is believed that this is why ADC0 performed better then ADC2. Changing the operation to give some space between ADC triggers fixed the issue.

Are they using the same trigger?What is your configuration?

In the reference manual, there is a description for two different cases. One case, configures the trigger sources separately, while the second uses the same trigger for the ADC modules.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------