- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- デジタルシグナルコントローラ

- :

- Re: SRAM for MC56F8367

SRAM for MC56F8367

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SRAM for MC56F8367

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Padma

It would be helpful to know how you have the SRAM chips connected to the DSC.

As Xiangjun Rong pointed out above, what CS lines are you using to access the SRAM.

A schematic or description would be good.

The example Code in CS_56F8367_PE.c (IN the attached file above) is very straightforward pointer access to memory:

These 2 lines define the location in memory (the second one could be SRAM).

unsigned int * IOPointer=(unsigned int *)0x0008010;

unsigned int * RAMPointer=(unsigned int *)0x0D10000;

These 2 lines write values to the locations.

(*IOPointer)=0x1234; //base address is 008 Hex in cpu bean

(*RAMPointer)=0x5678; //base address is D10 Hex

If you want to read from the locations you define a variable and then assign the value at the memory location to the variable.

Create the var.

unsigned int MemValue;

Assign a memory location value to the var.

MemValue = *RAMPointer;

So if RAMPointer had 0x5678 in it, now MemValue would have 0x5678 in it.

Hope this help some.

Pete

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Padma,

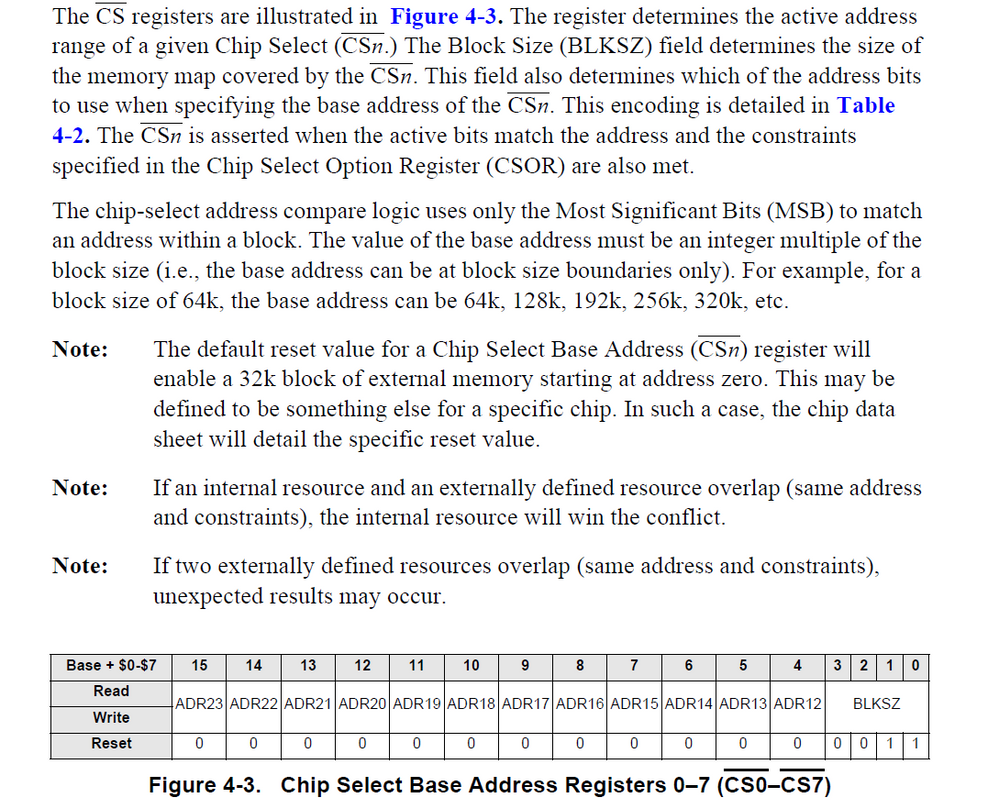

For detailed information about the Asynchronous SRAM, pls refer to the Chapter 4

External Memory Interface (EMI).

Pls refer to the figure 4-3, you use 128K*16 bits SRAM, the memory address is from A0~A16, the A17~A23 are used to decode the /CS signal. I suppose for example, you use /CS2 for one 128K SRAM, /CS3 for another 128K SRAM.

1)For /CS1, you can use the address:

A23 A22 A21 A20 A19 A18 A17 A16.................

0 0 0 1 1 1 1

You can access the 0x00 0000 to 0x 1E 0000 as the /CS2 address

You can set the Chip Select Base Address Registers 2 as 0x1E05

For /CS2, you can use the address:

A23 A22 A21 A20 A19 A18 A17 A16.................

0 0 0 1 1 1 0

You can access the 0x00 0000 to 0x1C 0000 as the /CS3 address

You can set the Chip Select Base Address Registers 2 as 0x1C05

For the other register, you can set based on your requirement.

You can PE to set the EMI register.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Thankyou. Still i find difficulties while programming as i have not used sram before.

Kindly can you send me a simple program to write a data and read that same data from sram.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

There is no example code for mc56f8367 SRAM module in codewarrior 11.1 package.