- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- Digital Signal Controllers

- :

- Re: Fault Filter in eflexPWM

Fault Filter in eflexPWM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

This is about Fault Filter in eflexPWM. Based on MC56F8036 where IPBus clock is 96MHz, PWMA_FFILTn is configured as 0x713 so filter time should be (7+3)*19/96=1.98us. But FFLAG is still set as 1 when input fault pin with a square wave and the width is 1.8us. Is is normal or something wrong?sutter

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

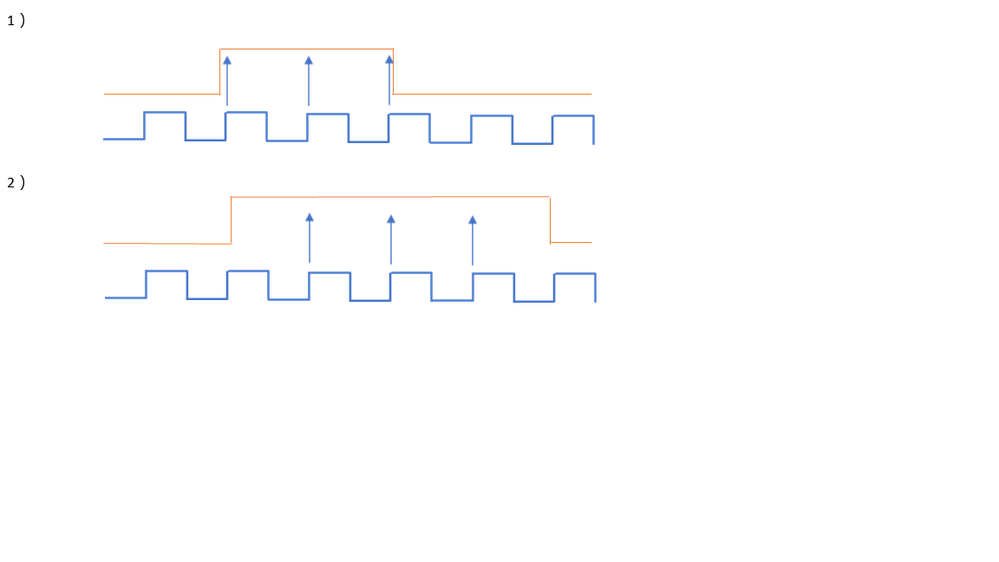

This phenomenon is quite reasonable. The fault filter works in a way like this: there's an internal high frequency clock F_filt for detecting the input voltage level, say if the input voltage stays one within continuous N periods of F_filt, the input is deemed to be one. For instance, suppose the input voltage is examined at each rising edge of F_filt, and N is set to 3, now see the attached pictures, the red waveform is the input signal on fault pin, and the blue one is F_filt. Both situation 1 and 2 can pass the filter, there's an error of +/- one period of F_filt.

In the case of 8036, F_filt is 96MHz/19 = 5.05MHz, so the period of F_filt is about 0.2us, which applies to your case.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This phenomenon is quite reasonable. The fault filter works in a way like this: there's an internal high frequency clock F_filt for detecting the input voltage level, say if the input voltage stays one within continuous N periods of F_filt, the input is deemed to be one. For instance, suppose the input voltage is examined at each rising edge of F_filt, and N is set to 3, now see the attached pictures, the red waveform is the input signal on fault pin, and the blue one is F_filt. Both situation 1 and 2 can pass the filter, there's an error of +/- one period of F_filt.

In the case of 8036, F_filt is 96MHz/19 = 5.05MHz, so the period of F_filt is about 0.2us, which applies to your case.