- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- ColdFire/68K Microcontrollers and Processors

- :

- ADC module results for MCF52259

ADC module results for MCF52259

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC module results for MCF52259

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm testing and analyzing an old project that was built within codewarrior for 7.2 arch and uTasker1.3. So I'm using uTasker ADC libraries. Viewing the adc results and de micro datasheets I have some unclear adc behaviour. I write hoping someone here could bring me some light if I missunderstanding something. The code has a single ended adc bit configured (ADC_0), loop mode and seq mode. Maybe is an uTasker issue. But I would like to have somethings about the MCU's adc cleared.

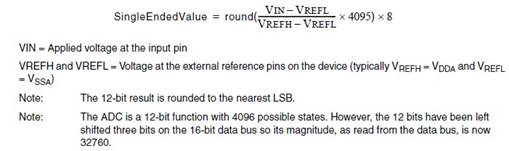

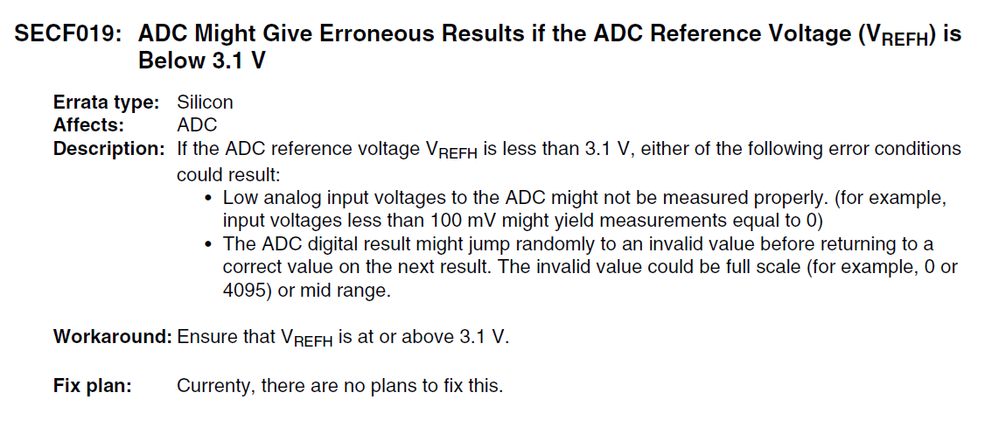

- Reading the datasheet I see that VRefH max could be typically 3.3v. If adc resolution is 12b, I will have 4092 points. This means the maxim value that I can read in result registers is 4092, being equivalent to maximum voltatge input = 3.3V. Isn't it?

- Is there any way to get more than 4092 value? I'm reading 21045, for example, so far from 4092!.

- Another question I have regarding the ADC block is if it is possible to have much more than 3.3 V to be converted? 5v, 10v, ... ,12v? Since I have understood, Vi converted rank depends on adc VREF max (3.3). But maybe I'm wrong. Could someone validate this?

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have just found this information in datasheet for the single ended mode. I think Note 2 and thie following formula would bring some sense to the values I was reading:

So, 111111111111000 is the max ADC value, and 0 when Vin = VREFL (with 4096 possible states between both).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

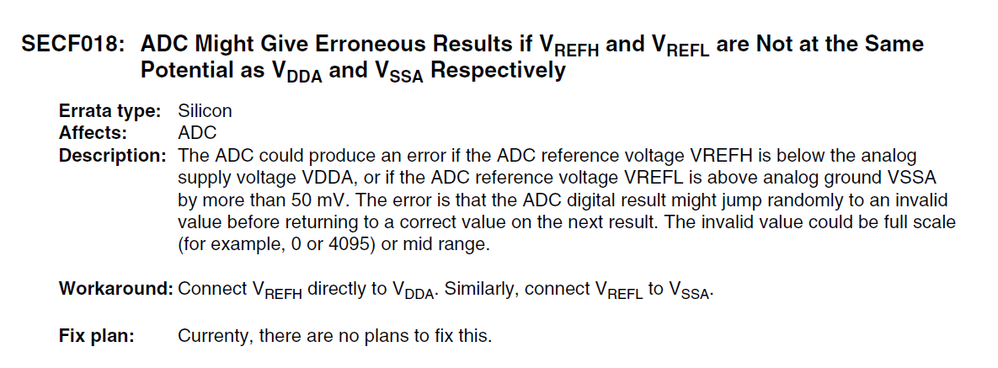

You did not mentioned any hardware board you used. The NXP evaluation board or customer board. I am not familiar with the uTasker, however I will try to clarify the ADC itself.

First please make sure that

So you should strictly follow the above ADC spec to get an accurate/full range of ADC value, the full scale should be 4095. So back to your questions:

1. yes, 3.3v with a full scale of 4095.

2. No.

3. VREFL<VADIN<VREFH