- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- Re: 36-bit memory assignment in Codewarrior

36-bit memory assignment in Codewarrior

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

36-bit memory assignment in Codewarrior

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

We designed a target board using p2020 CPU referring to the design of P2020RDB-PC. I must use 36-bit memory map in my target board.

Before I flash uboot to my target board, I tried to flash official 36bit-uboot to the P2020RDB-PC.

I modify relevant memory addresses in P2020RDB-PC_init_sram_flash.tcl, as following:

mem [CCSR 0xc08] = 0x00Fff000

mem [CCSR 0xca8] = 0x00Ff8000

mem [CCSR 0x0] = 0x00Fe0000

reg ${CAM_GROUP}L2MMU_CAM1 = 0x500003CAFC08000FE000000FE0000001

reg ${CAM_GROUP}L2MMU_CAM2 = 0x70000FCAFC08000FFF00000FFF000001

reg ${CAM_GROUP}L2MMU_CAM7 = 0x500003CAFC08000FF800000FF8000001

reg ${SPR_GROUP}HID0 = 0x00004080

reg ${SPR_GROUP}MAS7 = 0x0000000F

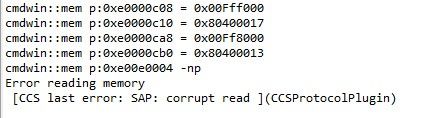

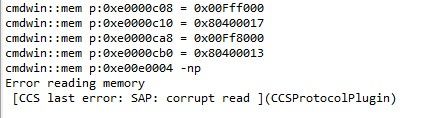

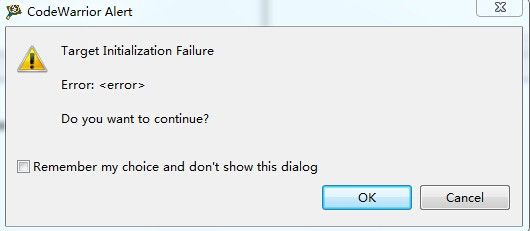

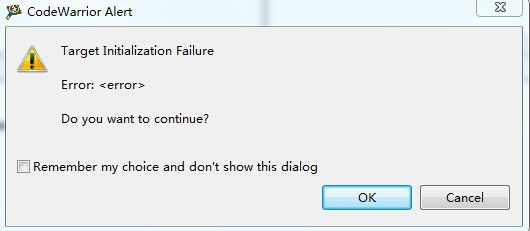

When I debug the initialization file, the console information is as followed:

What mistakes have I made in my .tcl file?

Thanks a lot

Best regards,

Min Zhao

Original Attachment has been moved to: P2020RDB-PC_init_sram_flash.tcl.txt.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First I think you could use P2020RDB-PC_init_sram_flash.tcl to initialize your customize target board and flash u-boot.(Probably you only need to modify the address for NOR Flash)

In you want to modify the initialization file to coincide with the 36bit address space, please pay attention to the following.

1. MMU TLB configuration, please note effective addresses are 32 bit, please refer to the table "e500v2 TLB1 Registers" in CW_PA_v10.3.3\PA\Help\PDF\Targeting_PA_Processors.pdf.

# MMU initialization

# define 256KB TLB1 entry 3: 0x00000000 - 0x0003FFFF; for internal chip SRAM

reg ${CAM_GROUP}L2MMU_CAM3 = 0x400001C0FC0800000000000000000001

# define 1MB TLB1 entry 1: 0xE0000000 - 0xE00FFFFF; for CCSR Space, non cacheable

reg ${CAM_GROUP}L2MMU_CAM1 = 0x500003CAFC080000E0000000E0000001

# define 16MB TLB1 entry 2: 0xFFF000000 - 0xFFFFFFFF; for Local Bus, cache inhibited

reg ${CAM_GROUP}L2MMU_CAM2 = 0x70000FCAFC08000FFF000000FF000001

# define 1MB TLB1 entry 7: 0xFF8000000 - 0xF80FFFFF; for NAND, cache inhibited

reg ${CAM_GROUP}L2MMU_CAM7 = 0x500003CAFC08000FF8000000F8000001

2. For CCSRBAR, please configure as the default

mem [CCSR 0x0] = 0x000e0000

set CCSRBAR 0xe0000000

Your configuration is correct, but if specifying variable CCSRBAR as 0xfe0000000, there is some problem in the tcl script to compute the value more than 32bit.

Attached an initialization file I modified based on yours.

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have flash 36bit-uboot to the custom p2020rdb-pc successfully by the tcl you gave to me.

Then I modified the tcl to math with my target board.But when I modified theR L2SRBAEA0

mem [CCSR 0x20104] = x00000000--------->0x0000000f

It failed to flash the uboot.

Then I use the mem [CCSR 0x20104] = 0x00000000, it worked.

Did that mean I should set the L2SRBAEA0 at 0x00000000?

And as you suggested, I need to modify NOR/NAND BR registers with 36bit physical addresses?

How should I modify NOR/NAND BR registers? what should I refer to NOR/NAND BR registers

Thanks a lot.

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

[CCSR 0x20104] should be 0x00000000, the physical address of SRAM is 0_00000000 and effective address is 00000000, in this initialization file DDR SDRAM is not considered about, and L2 to SRAM is the replacement of DDR, please refer to MMU TLB1 entry 3 is also configured like this.

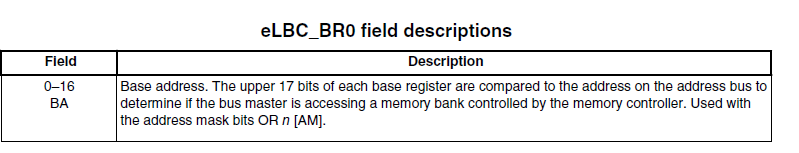

About BA of BR register configuration, I think I made a mistake, it should be the upper 17bits of 32 bit address.

For details,please refer to eLBC_BRn and ORn in P2020RM.

The following is u-boot code, you could have a reference.

#define CONFIG_SYS_FLASH_BASE 0xef000000

#ifdef CONFIG_PHYS_64BIT

#define CONFIG_SYS_FLASH_BASE_PHYS 0xfef000000ull

#else

#define CONFIG_SYS_FLASH_BASE_PHYS CONFIG_SYS_FLASH_BASE

#endif

#define CONFIG_FLASH_BR_PRELIM (BR_PHYS_ADDR(CONFIG_SYS_FLASH_BASE_PHYS) | BR_PS_16 | BR_V)

#define CONFIG_FLASH_OR_PRELIM 0xff000ff7

#define BR_PHYS_ADDR(x) ((u32)(x) & 0xffff8000)

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

On the base of my 4G DDR, need I modify the following addresses in u-boot code:

| #define CONFIG_SYS_INIT_L2_ADD | 0xf8f80000 |

| #define CONFIG_SYS_TEXT_BASE | 0xf8f82000 |

| #define CONFIG_SYS_TEXT_BASE | 0xeff80000 |

| #define CONFIG_RESET_VECTOR_ADDRESS | 0xeffffffc |

| #define CONFIG_SYS_CCSRBAR | 0xffe00000 |

They didn't have the judgment statement: #ifdef CONFIG_PHYS_64BIT

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Min Zhao,

I don't think you need to modify these addresses in u-boot, please refer to the following memory map for P2020RDB 36 bit physical addresses allocation in u-boot, probably you need to modify the Flash base address according to your target.

Start Physical Address | End Physical Address | Definition | Size |

0x000000000 | 0xbffffffff | DDR | 48G |

0xc20000000 | 0xc3fffffff | PCI Express 2 MEM | 512MB |

0xc00000000 | 0xc1fffffff | PCI Express 1 MEM | 512MB |

0xfef000000 | 0xfefffffff | FLASH | 16M |

0xfffc00000 | 0xfffc3ffff | PCI IO range | 256K |

0xfff800000 | 0xfff8fffff | NAND | 1M |

0xfffe00000 | 0xfffefffff | CCSR | 1M |

0xfffa00000 | 0xfffafffff | CPLD | 1M |

0xfffb00000 | 0xfffb7ffff | vsc7385 switch | 1M |

0xfffd00000 | 0xfffd03fff | L1 for stack | 16K |

0xffff00000 | 0xffff7ffff | L2 SDRAM | 512K |

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried to modify the address of L2 to 0xf_f8f80000 and the base address of CCSR to 0xf_ffe00000. But when I make it, there is an error in making start.o

| #define CONFIG_SYS_INIT_L2_ADDR | 0xff8f80000 |

| #define CONFIG_SYS_CCSRBAR | 0xfffe00000 |

How can I modify the base address of L2 and CCSR?

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In 36 bit u-boot, CCSRBAR has already been defined at 0xf_ffe00000.

Please pay attention to the following definition in include/mpc85xx.h.

#ifndef CONFIG_SYS_CCSRBAR_PHYS_HIGH

#ifdef CONFIG_PHYS_64BIT

#define CONFIG_SYS_CCSRBAR_PHYS_HIGH 0xf

#else

#define CONFIG_SYS_CCSRBAR_PHYS_HIGH 0

#endif

CONFIG_SYS_TEXT_BASE and CONFIG_RESET_VECTOR_ADDRESS are 32 bit effective addresses, please don't touch them.

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have replaced our 4G DDR to the official 1G DDR chip, and we successfully boot the board.

Did it mean I only need modify the configurations of DDR in u-boot matching to our 4G DDR on the base of above? What's more I don't need to modify anything else codes as long as I make 36-bit u-boot?

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Min Zhao,

Please pay attention to LAW size configuration and TLB configuration.

In the file include/configs/p1_p2_rdb_pc.h

#define CONFIG_SYS_SDRAM_SIZE_LAW LAW_SIZE_1G

In the file board/freescale/p1_p2_rdb_pc/tlb.c

| SET_TLB_ENTRY(1, CONFIG_SYS_DDR_SDRAM_BASE, CONFIG_SYS_DDR_SDRAM_BASE, | |

| MAS3_SX|MAS3_SW|MAS3_SR, 0, | |

| 0, 8, BOOKE_PAGESZ_1G, 1), |

Please note, the effective address is 32 bit, total 4 G memory space.

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have modify the codes as following:

#define CONFIG_SYS_SDRAM_SIZE_LAW LAW_SIZE_4G

SET_TLB_ENTRY(1, CONFIG_SYS_DDR_SDRAM_BASE, CONFIG_SYS_DDR_SDRAM_BASE,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 8, BOOKE_PAGESZ_2G, 1),

SET_TLB_ENTRY(1, CONFIG_SYS_DDR_SDRAM_BASE + 0x40000000,

CONFIG_SYS_DDR_SDRAM_BASE + 0x40000000,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 9, BOOKE_PAGESZ_2G, 1),

But it still showed 2GB umapped.

Do I need to modify more configurations?

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think it is fine to map 2G DDR memory, because total 4G effective memory space, and it is needed to leave another 2G for other devices. It is necessary to leave part of DDR memory unmapped.

Please refer to "Memory map" section in include/configs/p1_p2_rdb_pc.h.

Please make sure DDR memory allocation is not overlapped with other devices.

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My memory map is DDR 0x00000000 ~ 0xffffffff, other's all use the default 36-bit.

There is only L2's base address must be 32-bit(0xf8f80000).

Is this the reason of it?

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now we talk about effective addresses(32bit), please don't make it confused with physical addresses(36bit).

The following is the memory map of effective address, and for the physical addresses, please refer to the above table I pasted previously.

/*

* Memory map

*

* 0x0000_0000 0x7fff_ffff DDR Up to 2GB cacheable

* 0x8000_0000 0xdfff_ffff PCI Express Mem 1.5G non-cacheable(PCIe * 3)

* 0xec00_0000 0xefff_ffff NOR flash Up to 64M non-cacheable CS0/1

* 0xf8f8_0000 0xf8ff_ffff L2 SRAM Up to 512K cacheable

* (early boot only)

* 0xff80_0000 0xff80_7fff NAND flash 32K non-cacheable CS1/0

* 0xff98_0000 0xff98_ffff PMC 64K non-cacheable CS2

* 0xffa0_0000 0xffaf_ffff CPLD 1M non-cacheable CS3

* 0xffb0_0000 0xffbf_ffff VSC7385 switch 1M non-cacheable CS2

* 0xffc0_0000 0xffc3_ffff PCI IO range 256k non-cacheable

* 0xffd0_0000 0xffd0_3fff L1 for stack 16K cacheable

* 0xffe0_0000 0xffef_ffff CCSR 1M non-cacheable

*/

If needed, please read "Memory Management Units" in e500 core reference manual(E500CORERM.pdf).

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm a little confused. Do you mean the effective address of DDR is only up to 2G, and the effective address is translated to 4G by tlb1?

Then how should I set CONFIG_SYS_SDRAM_SIZE_LAW LAW_SIZE? and did I successfully modify the code in tlb.c?

Best regards,

Min Zhao