- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- QorIQ T1040 DIFF_SYSCLK internal termination

QorIQ T1040 DIFF_SYSCLK internal termination

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

According to T1040 Family Datasheet, there is an internal 100-Ohm termination at DIFF_SYSCLK input.

In my custom T1040-based board I'm observing two rather different waveforms at DIFF_SYSCLK_P pin.

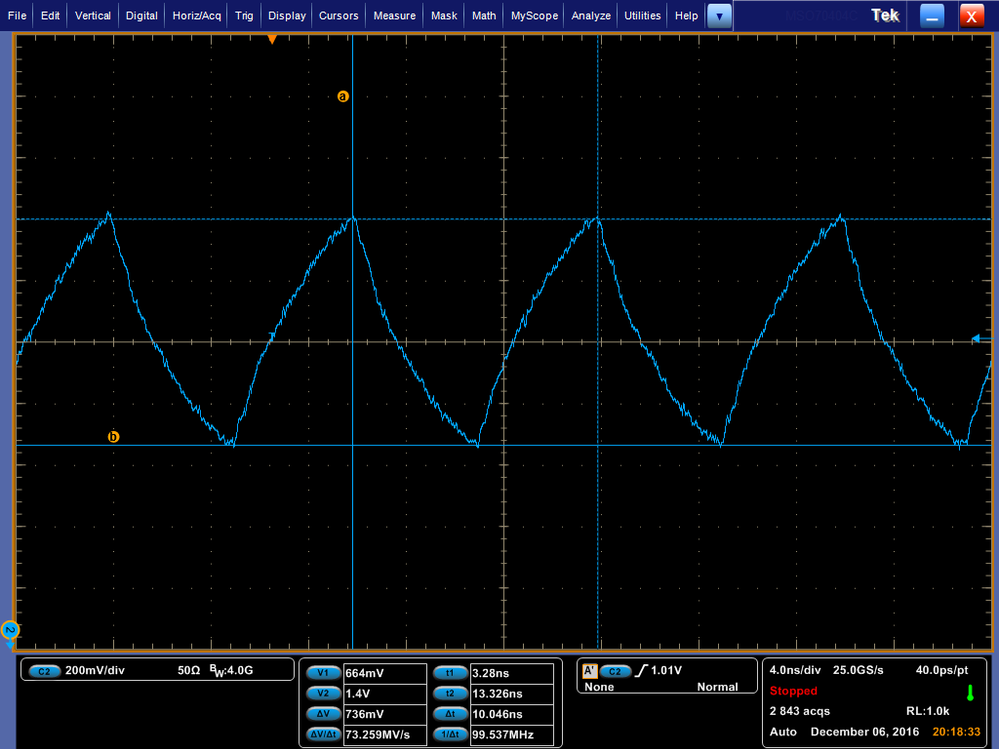

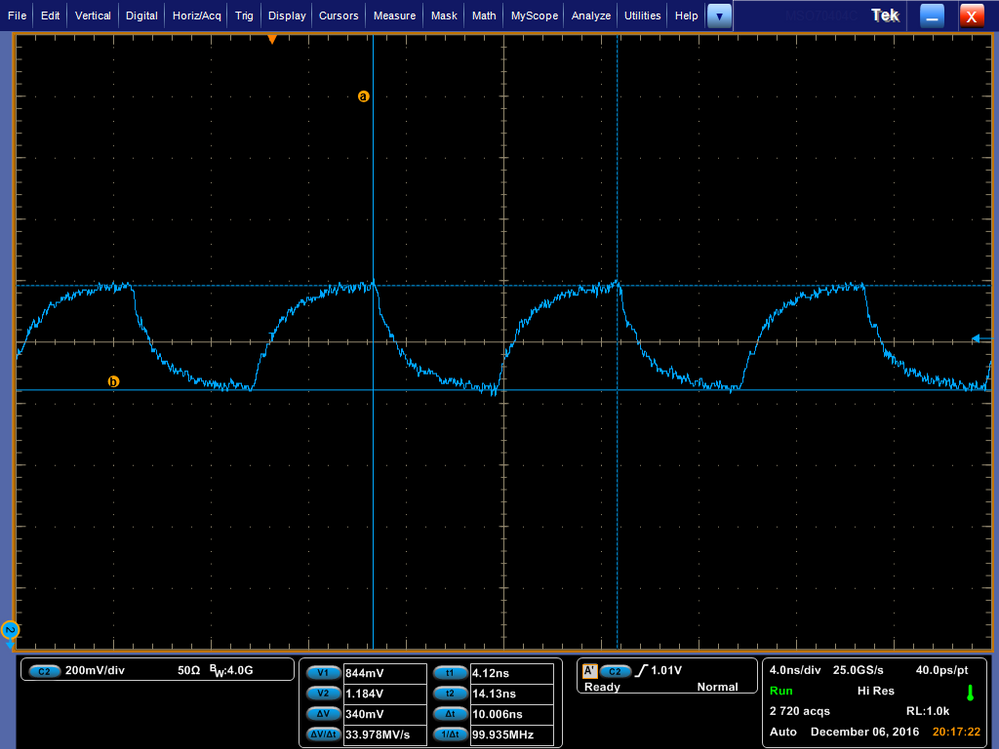

The first is for my default setup - SYSCLK is not used and pulled to ground:

The second is for reworked board where both SYSCLK and DIFF_SYSCLK are connected to the clock source:

DIFF_SYSCLK was selected as the clock input to the chip in both cases. Clock source is CDCM6208 in LVDS mode.

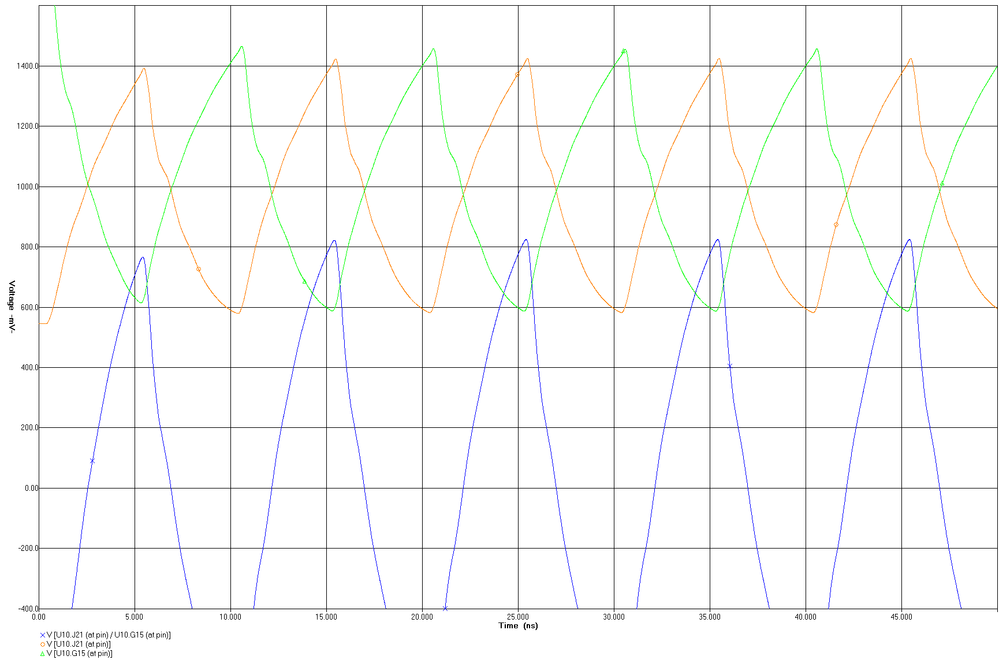

Next two pictures show DIFF_SYSCLK at T1040 pins (red/green - SE, blue - Diff) simulated with HyperLynx - unterminated at the CPU end:

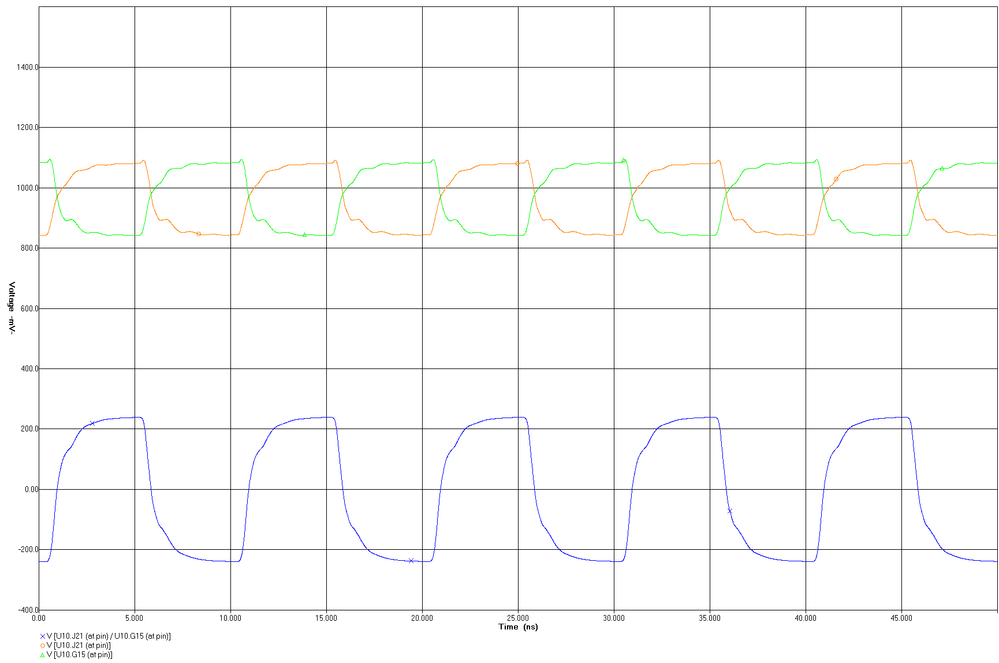

... and with internal 100-Ohm termination:

Please confirm that SYSCLK input must be connected to the clock source in order to enable internal termination at the DIFF_SYSCLK pins.

What another negative effects might be expected if SYSCLK is not connected?

BR,

Denis

(P.S. There is the discussion of T1024 DIFF_SYSCLK termination)

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Serguei,

These pins (cfg_eng_use) have very poor and somewhere inconsistent description through the documentation.

In particular, there's misguiding note in datasheet for all three of cfg_eng_use pins (note 21 at page 46):

"This pin should have an optional pull down resistor on board. This is required to support DIFF_SYSCLK/DIFF_SYSCLK_B".

(There's the same note in T1024 DS)

Some hours of experimentation showed that the internal termination is activated if (and only if) all conditions are met:

1) CPU is out of POR (i.e. PORESET_B is deasserted) or SYSCLK is applied; Обновлено

2) cfg_eng_use0 is pulled down;

3) cfg_eng_use1 and cfg_eng_use2 both pulled up (not down) at the moment of PORESET_B deassertion. Обновлено

BR,

Denis

Новое

These pins (cfg_eng_use) must be in a valid state not only at the moment of POR deassertion, but all the time during the PORESET_B assertion!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Serguei,

These pins (cfg_eng_use) have very poor and somewhere inconsistent description through the documentation.

In particular, there's misguiding note in datasheet for all three of cfg_eng_use pins (note 21 at page 46):

"This pin should have an optional pull down resistor on board. This is required to support DIFF_SYSCLK/DIFF_SYSCLK_B".

(There's the same note in T1024 DS)

Some hours of experimentation showed that the internal termination is activated if (and only if) all conditions are met:

1) CPU is out of POR (i.e. PORESET_B is deasserted) or SYSCLK is applied; Обновлено

2) cfg_eng_use0 is pulled down;

3) cfg_eng_use1 and cfg_eng_use2 both pulled up (not down) at the moment of PORESET_B deassertion. Обновлено

BR,

Denis

Новое

These pins (cfg_eng_use) must be in a valid state not only at the moment of POR deassertion, but all the time during the PORESET_B assertion!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Denis,

yes, the power-up (POR) configurations pins are sampled on po-reset negation. I have known that some POR configurations must be set properly for the DIFF_SYSCLK/DIFF_SYSCLK_B termination - I’ve met already the same problem on some T1 device. But pins names I got from the QorIQ T1040, T1020 Data Sheet, Rev. 2, 06/2015. Sorry I copied IFC_WP0_B/cfg_eng_use2 instead of IFC_WE0_B/cfg_eng_use0 just by chance. However for these cfg_eng_use0/1 pins it says: “21. This pin has a weak (~20 kΩ) internal pull-up P-FET that is enabled only when the processor is in its reset state. This pin should have an optional pull down resistor on board. This is required to support DIFF_SYSCLK/DIFF_SYSCLK_B” Now I feel it sounds a little bit vague. But I concluded that only these 2 pins has to be pull down in order to support DIFF_SYSCLK/DIFF_SYSCLK_B. So it seems the data sheet should be clarified.

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have a great day,

There are 2 configuration pins IFC_OE_B/cfg_eng_use1 and IFC_WE0_B/cfg_eng_use0. These pins should have pull down resistors on board. This is required to support DIFF_SYSCLK/DIFF_SYSCLK_B. Did you pull-don these pin?

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------