- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Processors

- :

- i.MX Processors Knowledge Base

- :

- i.MX6 DDR Stress Test Tool V1.0.3

i.MX6 DDR Stress Test Tool V1.0.3

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

i.MX6 DDR Stress Test Tool V1.0.3

i.MX6 DDR Stress Test Tool V1.0.3

Note, the tools described in this page are deprecated and are no longer maintained. For the latest maintained i.MX 6/7 series DDR tools, the user can find these here:

i.MX 6/7 Series DDR Tool Release

Hi All,

DDR_Stress_Tester is a software application for fine tuning DDR parameters and verifying DDR performance on i.MX6 boards. It performs write leveling, DQS gating, read/write delay calibration on the target board to match the layout of the board and archive the best DDR performance.

In addition, the stress test can help the user to verify the DDR performance on their boards.

The following are the features supported:

• Support i.MX6Q, i.MX6D, i.MX6DL, iMX6S, i.MX6SL, and i.MX6SX DDR calibration.

• Support DDR3 write leveling, DQS gating, Read/Write Delay auto-calibration.

• Support LPDDR2 Read/Write Delay auto-calibration.

• Support 16 bits, 32 bits, and 64 bits data bus.

• Support fixed-mapping 2-channel LPDDR2.

• Support DDR stress test between the frequency 135MHz and 672 MHz

If USB OTG port is not available on customer board, please use the images in DDR_Stress_Tester_V1.0.3_UART1_for_SDboot&JTAG.zip.

The bin files in the packages can be loaded by uboot and elf files are used by JTAG load. Please note when the image is loaded by u-boot, the DDR is initialized by u-boot (reference flash_header.S).

To run ddr stress test from u-boot, CONFIG_SPLASH_SCREEN must be disabled in u-boot. Because when enter self refresh mode in ddr stress test, DRAM access will be blocked. If splash screen in u-boot is enabled, IPU will continuously access DRAM, so the system will hang up.

If you have other DMA access in u-boot, it must be disabled.

If customer uses different RX/TX pin for UART, please contact FAE.

| UART1 | 6DQ | 6DL | 6SL | 6SX |

|---|---|---|---|---|

| TX | CSI0_DAT10/ALT3 | CSI0_DAT10/ALT3 | UART1_TXD/ALT0 | GPIO1_IO04/ALT0 |

| RX | CSI0_DAT11/ALT3 | CSI0_DAT11/ALT3 | UART1_RXD/ALT0 | GPIO1_IO05/ALT0 |

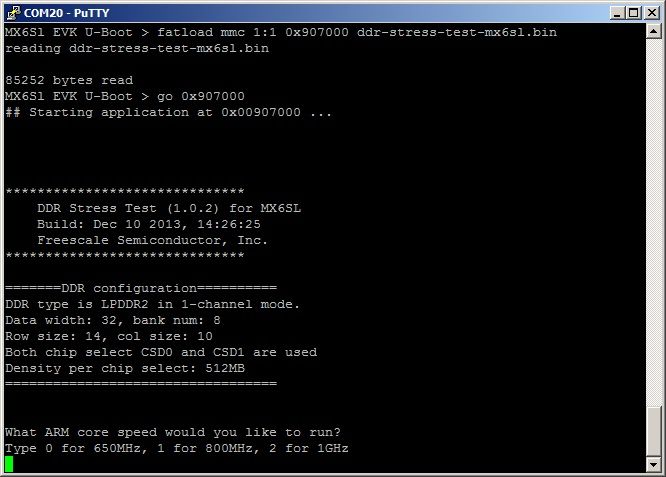

The commands to run ddr test in i.MX6Q uboot:

U-Boot > fatload mmc 2:1 0x907000 ddr-stress-test-mx6dq.bin

U-Boot > go 0x907000

For i.MX6Q/6D 4K interleaved LPDDR2, please use version v1.0.3.1.

i.MX6 DDR Stress Test Tool V1.0.3.1 for LPDDR2 4K interleaved mode

For i.MX6/i.MX7 DDR Stress Test Tool with GUI interface, please use version V2.x:

i.MX6/7 DDR Stress Test Tool V2.10

History

V1.0.3: i.MX6SoloX is supported.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

i.Mx6DQSDL DDR3 Script Aid

https://community.freescale.com/docs/DOC-94917

i.Mx6DQSDL LPDDR2 Script Aid

https://community.freescale.com/docs/DOC-95089

i.Mx6SL LPDDR2 Script Aid

https://community.freescale.com/docs/DOC-94987

How to tune the CA delay line in LPDDR2?

There is no auto CA calibration provided, we can only fine tune it manually.

1. Adjust CA delay line from 0x00000000, 0x00100000, 0x00200000..to 0x007f0000 (with the step of 0x10) , run stress test with each value (using auto calibration or default WR/RD delay line setting)

2. Given that the CA delay line setting which pass stress test is 0x00200000, 0x00300000, and 0x00400000

3. We can try 0x00180000 and 0x00480000, to find a more accurate boundary.

4. After above trial, we can set the CA delay line to the middle of “pass” window.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

We're using i.Mx6DL and LPDDR2 single channel, starting at 0x10000000 (DDR Memory Map Config = '00'). Does this version select the correct address (i.e. not 0x80000000) for our setup?

I'm asking because it automatically says "CHANNEL0 is selected." and for previous version 0.042 we had to manually select channel1 to "trick" stress test into using start address 0x10000000.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Emil Myhrman,

Please use version 1.0.1. For i.MX6DQ, the DDR mapping start address is configured as chapter "2.3 DDR mapping to MMDC controller ports" in i.MX 6Dual/6Quad Applications Reference Manual.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Got the program working now, thank you very much!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello,

I tried to run the DDR3 Stress Tester but the application crashes after printing a single line:

MX6DQ opened.

We are using an i.MX6D7CVT08AC (Industrial, 800MHz) and the PC is running Windows 7 Home Premium SP1 64bit.

From Linux I'm able to run the imx_usb_loader application and download an image which toggles an LED connected to GPIO2[4].

Regards

Matthias Mann

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

We got the Stress Tester running. The tool doesn't like when you give it the wrong input file :smileyhappy:

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello,

I do not have the USB OTG port available on my custom board, is it possible to load this stress tester application directly via sd card and u-boot?

Thanks

Brent

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Brent,

The image in DDR_Stress_Tester_V1.0.1.zip can't be loaded through sd card. I just attached image DDR_Stress_Tester_V1.0.1_UART1_for_SDboot&JTAG.zip. The bin files in the packages can be loaded by uboot and elf files are used by JTAG load. Please note when the image is loaded by u-boot, the DDR is initialized by u-boot.

Regards,

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Thank you Grace, that is excellent! Thanks very much for your help! I will update on how it works.

Regards

Brent

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

The entry point is 0x907000 if anyone needs it.

(o:

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Grace...

It loads well, and I can interact with u-boot of course, but I cannot interact with this application.

My rx/tx in u-boot are :

/* UART1 TXD */

mxc_iomux_v3_setup_pad(MX6Q_PAD_SD3_DAT6__UART1_RXD);

/* UART1 RXD */

mxc_iomux_v3_setup_pad(MX6Q_PAD_SD3_DAT7__UART1_TXD);

Is this stress test tool open source?

******************************

DDR Stress Test (1.0.1) for MX6DQ

Build: Oct 21 2013, 14:05:09

Freescale Semiconductor, Inc.

*****************************

=======DDR configuration==========

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 15, col size: 10

Chip select CSD0 is used

Density per chip select: 2048MB

==================================

What ARM core speed would you like to run?

Type 0 for 650MHz, 1 for 800MHz, 2 for 1GHz, 3 for 1.2GHz

--> System does not respond to my input here.

Thanks

Brent

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Brent, the tx/rx PIN of MX6Q SabraSD board is CSI0_DAT10 and CSI0_DAT11.

/* UART1 TXD */

writel(ALT3, IOMUXC_SW_MUX_CTL_PAD_CSI0_DAT10);

/* UART1 RXD */

writel(ALT3, IOMUXC_SW_MUX_CTL_PAD_CSI0_DAT11);

We understand the customer may use different rx/tx pin for UART, that is the reason we only release DDR stress tool which uses USB port for user input and output for general release.

Please submit your request to FSL CRM system.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Thanks Grace.

It is my lucky day since I was using DAT10/11 for SPI2 but I have test-points on those two pads so I tested them them temporarily for UART.

It works (o; Not FSL CRM request is required.

Thanks very much!

Brent

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi, the board I am working on does not have USB OTG either, and doesn't use UART port 1 but ports 3&4 instead.

Is there a way to access the sources or get elf files where other uart ports would be used ?

Thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Thierry,

We don't want to release the binary for specific customer here. Please contact your FAE and send your request to FSL.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

To run ddr stress test from u-boot, CONFIG_SPLASH_SCREEN must be disabled in u-boot.

Because when enter self refresh mode in ddr stress test, DRAM access will be blocked. If splash screen in u-boot is enabled, IPU will continuously access DRAM, so the system will hang up.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi.

I am trying to run the tool on SabreSD Board.

Once I start the tool it is getting stuck on "Downloading image to IRAM ok"

At that point HID device in device manager is disappeared and Usb Input device with "Failed to start (code 10)" appears.

After a while Stress Tool times out and extits.

I am using 64-bit Windows 7 SP1

Any ideas?

Thanks.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

does the Host USB driver now support a 64Bit version Windows?

Greetings

Andreas

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Great tool that works well on my Nitrogen6! I am wondering if it is possible (for a future version) to read the temperature of the cpu during the stress test for instance?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Grace - can you let me know where the source code for version 1.0.2 is located internally? The link we were given previously goes to version 1.0 and not further. Thanks!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi

I used this stress test with our custom board.

However, the following error log was output.

=====

Would you like to run the DQS gating, read/write delay calibration? (y/n)

Starting DQS gating calibration...

. . . . . . . . . . . . . . ERROR FOUND, we can't get suitable value !!!!

dram test fails for all values.

=====

Could you let me know what is wrong in this case?

(e.g. Circuit pattern is too bad, setting value in .inc file is incorrect, etc...)

Best Regards,

Mar 14, 2014

Satoshi Shimoda

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Grace,

I am not having much luck using v1.02 of this tool. The test script generated by the spreadsheet here i.Mx6DQSDL DDR3 Script Aid starts off with a 'setmem /16 0x020bc000 = 0x30' to disable the watchdog, which the stress tool complains about:

.\DDR_Stress_Tester_V1.0.2\Binary>DDR_Stress_Tester.exe -t mx6x -df mt41k128m16-125_1066mhz_4x128x16.inc

MX6DQ opened.

dcd address 0x020bc000 out of valid range.

the addr out of valid range.

I see that this specific write is commented out in some of the provided sample scripts so I comment it out in my script and the tool does indeed continue on but it seems like the tool locks up within 30 seconds which to me feels an awful lot like the board perhaps resetting from a watchdog timeout? The tool doesn't hang at a specific spot... it just seems to hang within 30 seconds. I can't type fast enough to get past entering in MR1 for the write-leveling test.

Any ideas?

Is there source for this tool available somewhere? This seems like a great tool but its horrible that it isn't distributed with sourcecode so people could work around some of the above issues.

Thanks,

Tim

partner

i.mx6

gateworks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Please set the WALAT value on MMDCx_MDMISC register to 1 in the initialization script and re-run the DDR_Stress_Tester.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Grace,

Thank you for your reply.

Unfortunately, I have set WALAT on MMDCx_MDMISC register to "1" as following.

setmem /32 0x021b0018 = 0x00011740 // MMDC0_MDMISC

Is there any other point I have to check?

Or is this issue hardware layout?

Best Regards,

Mar 17, 2014,

Satoshi Shimoda

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

That may be caused by the hardware layout.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Tim

In Reference Manual of i.MX 6Dual/6Quad, chapter 2 memory map, you can see the valid MMDC range is from 0x021B0000 to 0x021B7FFF. So your address 0x020bc000 is out of range.

021B_0000 021B_3FFF MMDC (port 0) 16 KB

021B_4000 021B_7FFF MMDC (port 1) 16 KB

You can contact your FAE or marketing to get the source code.

Regards,

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello Grace,

I used the bin files included in "DDR_Stress_Tester_V1.0.1_UART1_for_SDboot&JTAG.zip" for calibrate and test the DDR3 memories on my custom mx6 board.

For my board with quad-core, I fixed 0x907000 as entry-point and the program was executed correctly.

For my board with single-core, I fixed the same entry-point but the program don't run...

Please, can you help me?

Thank you very much.

Regards

Andrea

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

You can check whether the UART of customer board is same as 6SL EVK board.

/* UART1 TXD */

writel(ALT0, IOMUXC_SW_MUX_CTL_PAD_UART1_TXD);

/* UART1 RXD */

writel(ALT0, IOMUXC_SW_MUX_CTL_PAD_UART1_RXD);

// daisy chain setup

writel(0x0, IOMUXC_UART1_IPP_UART_RXD_MUX_SELECT_INPUT);

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello Grace,

Thank youmfor your answer.

In my board with iMX6 solo (not solo-lite) the debug console is placed on CSI0_DAT10 and CSI0_DAT11; then it is not compatible with the .bin test...

I tried to use the test in USB version, but on my PC I have the same problem highligted by Gevorg Sargsyan (22-gen-2014 21.47)...

Nothing to do...

Best regards

Andrea

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

I have this same issue with mine. When I had the excel sheet auto generate the .inc file for my board setup it has a line;

//=============================================================================

// Disable WDOG

//=============================================================================

setmem /16 0x020bc000 = 0x30

I noticed in one of the example files that that line is commented out. When I comment it it seems to work great. I am just wondering what that line is suposed to do and why the stress tester errors. If i under stand it should just disable the watch dog timer but not sure. Should I be commenting this line out?

Thank

Michael

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Michael,

The excel sheet generates the inc file for JTAG mode. For USB download mode, you need comment out setmem /16 0x020bc000 = 0x30.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Grace.

For me it hangs after;

Calibration will run at DDR frequency 528MHz. Type 'y' to continue.

If you want to run at other DDR frequency. Type 'n'

Could this be because of the CONFIG_SPLASH_SCREEN, which I should have disabled?

Or do we also need to initialize the registers according to the .inc file (parameters from the excel document) when starting up u-boot?

If I need to initialize the register, do I initialize all registers from the excel document, before I run the stress test? (I noticed that some are initialized 2, for instance 0x21b0004)

Thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

I managed to get the stress to run from u-boot.

I had to make sure that IPU wasn't initialized.

But now I getting stuck on the calibration test, getting error: ERROR FOUND, we can't get suitable value!!!!

Any suggestions?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Grace! How are you? I use the bin files from "DDR_Stress_Tester_V1.0.1_UART1_for_SDboot&JTAG.zip", but the program hangs when it calibrates the memory. I'm using Freescale Sabre SD board.

----->

MX6Q SABRESD U-Boot > go 0x907000

## Starting application at 0x00907000 ...

******************************

DDR Stress Test (1.0.2) for MX6DQ

Build: Dec 10 2013, 14:26:05

Freescale Semiconductor, Inc.

******************************

=======DDR configuration==========

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 14, col size: 10

Chip select CSD0 is used

Density per chip select: 1024MB

==================================

What ARM core speed would you like to run?

Type 0 for 650MHz, 1 for 800MHz, 2 for 1GHz, 3 for 1.2GHz

ARM set to 800MHz

Please select the DDR density per chip select (in bytes) on the board

Type 0 for 2GB; 1 for 1GB; 2 for 512MB; 3 for 256MB; 4 for 128MB; 5 for 64MB; 6 for 32MB

For maximum supported density (4GB), we can only access up to 3.75GB. Type 9 to select this

DDR density selected (MB): 1024

Calibration will run at DDR frequency 528MHz. Type 'y' to continue.

If you want to run at other DDR frequency. Type 'n'

<-----

Any suggestions?

Thanks!!

Ariel.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Ariel,

To run ddr stress test from u-boot, CONFIG_SPLASH_SCREEN must be disabled in u-boot.

Because when enter self refresh mode in ddr stress test, DRAM access will be blocked. If splash screen in u-boot is enabled, IPU will continuously access DRAM, so the system will hang up.

Please make sure there is no DMA running to access DRAM in u-boot.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Grace,

On my own design, i ran your DDR_Stress_Tester_V1.0.1_UART1_for_SDboot&JTAG.zip that worked for me (just to confirm the initial values from U-BOOT as i replicated the layout from Sabre SD board), just have observed that the SW levelling values are all above 0x2F :

MMDC_MPWLDECTRL0 ch0 after write level cal: 0x0046004B

MMDC_MPWLDECTRL1 ch0 after write level cal: 0x003C0043

MMDC_MPWLDECTRL0 ch1 after write level cal: 0x002B002B

MMDC_MPWLDECTRL1 ch1 after write level cal: 0x0029003F

As notified in the document, i modified the MDMISC value in my U-BOOT file (0x00001740 => 0x00011740) but nothing changed, does your programm erase my value with your own one and if so what is your value ? and can we keep the write leveling results as it ?

Patrick.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

In Chapter 5 FAQ of i.MX6 DDR Stress Tester User’s Guide

Do I need to update the DDR initialization script after running the calibration?

Yes. The calibration results are stored in the MMDC registers during the test only. It is suggested to update the initialization script and re-run the test on different boards to confirm the DDR performance and make sure the MMDC register settings are correctly ported to the firmware.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello,

Can anyone explain me how to load the binary file of DDR_Stress_Tester_V1.0.1_UART1_for_SDboot&JTAG.zip by u-boot? Is there any user guide for loading this from SD card? I want to run the DDR stress test to obtain the optimal DDR configuration.

Any help will be appreciated.

Yijun

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Thank you Grace for your quick answer.

Well, i understand that the results of the stress program have to be used to update the DDR3 initialisation process. In fact my question was not exactly this one as i don't use the the initialization script but only U-BOOT (i don't have JTAG access so i upload your binary file through TFTP). Here is how i proceed :

- I have my own U-BOOT relevant to my board

- The board boots on SD card

- I get the U-BOOT prompt

- I tftp the DDR_Stress_Tester_V1.0.1_UART1_for_SDboot&JTAG.zip binary program (DL in my case) on RAM (0x907000 as you mentioned above in the post)

- Go on this address

- Get the values that i mentionned previously

What i noticed is whatever is the value of MDMISC that i write in U-BOOT file (flash_header.s, ie 0x00001740 or 0x00011740), the values for the write leveling process are always above 0x2F so i was wondering if the binary DDR stress program was altering the MDMISC value i write in flash_header.s before launching the test by itself, which could explain why i get always the same value.

Best regards,

Patrick.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Patrick,

If you just want to do the stress test, you can skip the calibration. It is normal that write leveling calibration got consistent values. To understand write leveling, you can reference 45.11.6 Write leveling Calibration of reference manual.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

2

Hi Grace,

I'm assuming this stress test runs out of OCRAM, is that correct? If so, can you tell me what the keys are to accessing DDR RAM from OCRAM code? I'm getting a crash every time I try - the debugger completely chokes and won't give me any data. Do I still need to leave some hooks for the DDR in the linker script, for example?

I'm building a stripped down version of the Platform SDK, so I'm thinking the DCD and all should be set up correctly. Runs fine other than this external DDR access issue.

Just looking for some hints on a perplexing problem. Thanks.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

2

Turns out the code is fine and only the ARM DSTREAM debugger creates the problem for itself. Strange.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Is the tool or its alternative available for Vybrid processors?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

I am attempting to run the stress test tool on an EDM-IMX6 board manufactured by TechNexion (and a Wandboard) to try to resolve some intermittent memory corruption issues we have been seeing when using these boards.

When I run the write leveling calibration, the value for MMDC_MPWLDECTRL1 always comes back with an incorrect value (see output below).

My question is: Is this a problem with the stress test calibration tool, or is this indicative of a design problem on the board?

FYI, I have been unable to get this board to pass the stress test at 475Mhz (it fails almost immediately every time), though it passes at other frequencies, both higher and lower.

Thanks,

Tony

Would you like to run the write leveling calibration? (y/n)

Please enter the MR1 value on the initilization script

This will be re-programmed into MR1 after write leveling calibration

Enter as a 4-digit HEX value, example 0004, then hit enter

0004 You have entered: 0x0004

Start write leveling calibration

Write leveling calibration completed

MMDC_MPWLDECTRL0 ch0 after write level cal: 0x00130017

MMDC_MPWLDECTRL1 ch0 after write level cal: 0x0017000E

MMDC_MPWLDECTRL0 ch1 after write level cal: 0x000F001D

MMDC_MPWLDECTRL1 ch1 after write level cal: 0x017A0013

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Did I have to do write leveling calibration if I have no Fly-by layout config?

Because I always get:

Would you like to run the DQS gating, read/write delay calibration? (y/n)

Starting DQS gating calibration...

. . . . . . . . . . . . . . ERROR FOUND, we can't get suitable value !!!!

dram test fails for all values.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

For Fly-by layout, write leveling calibration is needed.

Grace

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

No we have no Fly-by layout we have T-routing...

Regards

Marcel

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Ok we have no Fly-by layout but what have I have to fill in at the write leveling data at the Excel sheet in the red cells?

Regards

Marcel

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello GraceSi,

We are working on developing test software for the i.MX6 board where we would like to include some of the test cases from the this DDR3 stress tool. Can we get the source of DDR_Stress_Tester_V1.0.3 tool?

Immanuel

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Immanuel,

Please contact your FAE or Marketing.

Grace