- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso Config Tools

- :

- clocks tool FRGCTRL_MUL value selection

clocks tool FRGCTRL_MUL value selection

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm trying to configure clocks for an LPCXpresso54018, SDK version is: SDK Version: KSDK 2.4.2 (2018-09-14).

I want to configure the FRG_clock.

The value for FRGCTRL_MUL is set to *256, and can't be changed. It's only possible to set FRGCTRL_DIV.

From the LPC540xx reference manual, it looks like FRGCTRL_DIV should always set to 0xff. But i should be able to set FRGCTRL_MUL.

I've added screenshots showing the dropdown menu's for both settings.

Am i doing something wrong? Or is it a problem in clocks tool?

thanks,

Cedric

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Cedric,

I have checked the implementation and it seems that there are selected confusing names of the divider and multiplier only. The clock model works properly.

If you look into reference manual (UM11060) you can find the following expression for computing the FRG clock:

Flexcomm Interface function clock = (clock selected via FRGCLKSEL) / (1 + MULT / DIV)

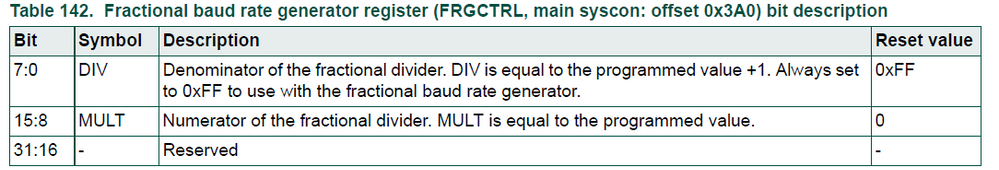

And also the following definition of the related bitfields:

It is mean that the MULT bitfield works as the divider and DIV bitfield works as the multiplier part of the fractional divider.

In the clock model (clock diagram) the FRGCTRL_MUL multiplier controls the DIV bitfield and must be 0xFF. The FRGCTRL_DIV divider controls the MULT bitfield (1+MULT/0xFF = (0xFF + MULT) / 0xFF), i.e. the divider provides values 256 - 511.

It means that the clock model works properly and provide the correct values in the FRGCTRL register (you can also check the bitfield values in the Registers window of the Clocks tool).

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Cedric,

I have checked the implementation and it seems that there are selected confusing names of the divider and multiplier only. The clock model works properly.

If you look into reference manual (UM11060) you can find the following expression for computing the FRG clock:

Flexcomm Interface function clock = (clock selected via FRGCLKSEL) / (1 + MULT / DIV)

And also the following definition of the related bitfields:

It is mean that the MULT bitfield works as the divider and DIV bitfield works as the multiplier part of the fractional divider.

In the clock model (clock diagram) the FRGCTRL_MUL multiplier controls the DIV bitfield and must be 0xFF. The FRGCTRL_DIV divider controls the MULT bitfield (1+MULT/0xFF = (0xFF + MULT) / 0xFF), i.e. the divider provides values 256 - 511.

It means that the clock model works properly and provide the correct values in the FRGCTRL register (you can also check the bitfield values in the Registers window of the Clocks tool).

Best Regards,

Marek Neuzil