- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX6UL: CCM_CLKO2 arm_clk_root on SD1_DATA2 pad

i.MX6UL: CCM_CLKO2 arm_clk_root on SD1_DATA2 pad

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

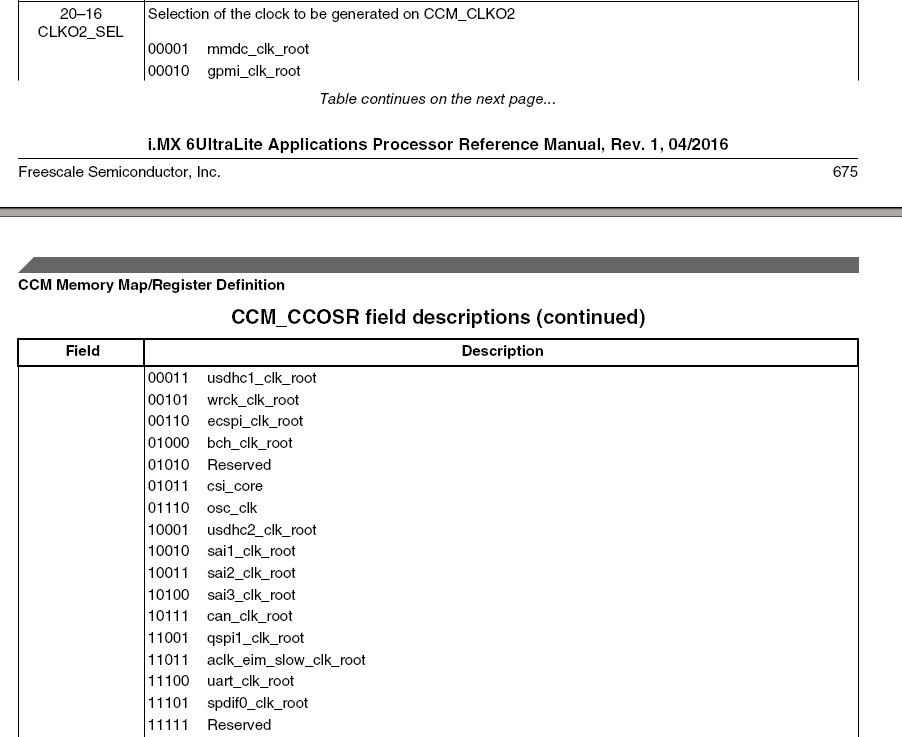

Hello, we are using the i.MX6UL platform and I need to observe the arm_root_clk on CCM_CLKO2 on the SD1_DATA2 pad as detailed in the RM. We are doing this because we need a visual representation of our operating frequency. My settings are as follows:

CCM Clock Output Source Register (CCM_CCOSR) (0x20C_4060h)

- set to value 0x018a0100

- this selects arm_root_clk for CLKO2 with divider of 5

SW_MUX_CTL_PAD_SD1_DATA3 SW MUX Control Register (IOMUXC_SW_MUX_CTL_PAD_SD1_DATA3) (0x20E_01D0h)

- set to value 0x00000006

- this selects ALT6 mode for CCM_CLKO2

SW_PAD_CTL_PAD_SD1_DATA3 SW PAD Control Register (IOMUXC_SW_PAD_CTL_PAD_SD1_DATA3) (0x20E_045Ch)

- set to value 0x0001F0D9

- this sets 200Mhz max pad freq

With these setting I am unable to see a clock on SD1_DATA2. If I change CCM_CCOSR to 0x010e0000 I will see the 24Mhz osc_clk correctly. I can also seem to see all other CLKO2 clocks - just not the one I need.

Is there something further I need to do to view the arm_clk_root clock?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi michaelschell

unfortunately i.MX6UL has not selection CLKO2_SEL= 01010 arm_clk_root,

it is reserved :

i.MX6UL Reference Manual

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6ULRM.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi michaelschell

unfortunately i.MX6UL has not selection CLKO2_SEL= 01010 arm_clk_root,

it is reserved :

i.MX6UL Reference Manual

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6ULRM.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks so much igor. Im clearly using the wrong version of the i.MX6UL reference manual. Mine does not show that value (01010) as reserved but instead specifies it for arm_clk_root. Ill move forward with this version of the RM. To your knowledge then, for the i.MX6UL, is there no way to export the arm clock (cpu clock rate) off chip?