- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Clock output at the SS switch of ECSPI of i.MX6Solo

Clock output at the SS switch of ECSPI of i.MX6Solo

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clock output at the SS switch of ECSPI of i.MX6Solo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

We connect three devices to ECSPI1 port.

We use fsl-yocto-3.10.53-1 .1.0.

The ECSPI driver remains a default.

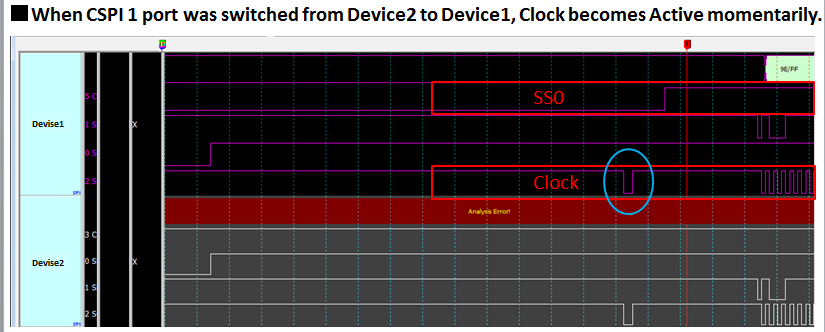

When ECSPI1 is switched from SS1(Device2) to SS0(Device1), a clock is output momentarily just before SS0 becomes active.

Why is a clock output?

The field setting of each register is the following

ECSPI1_CONREG

- CHANNEL MODE:1 (all master mode)

- SMC: 0

ECSPI1_CONFIGREG

- SCLK_CTL:1 (stay high)

- DATA CTL:0 (stay high)

- SS_POL:0 (Active Low)

- SS_CTL:1 (Negate Chip Select (SS) signal between SPI bursts)

- SCLK_POL:1 (Active low polarity)

- SCLK_PHA:1 (Phase 1 operation)

May I have advice?

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano can you help to continue with the follow up as priority?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano please continue with the follow up of this case.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuuki,

I have not seen this behavior before. Are you getting some kind of issue thanks to this glitch?

Can you share the steps to reproduce the problem and modifications you have performed to the BSP.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alejandro-san,

Thank you for your support.

Is there any sample code using HW SS function(not GPIO) as the SS signal?

Would you send it if there is it?

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuuki,

You can try to enable the native Chip select of the ECSPI module.

Please refer to this How to enable native and gpio cs on ecspi

The changes are performed in the dts file.

Please try that and let me know how it goes.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alejandrolozano-san,

We approach this problem by two methods to solve it.

- One is a method using native Chip select.

- Another is method avoiding a glitch with CS-GPIO.

[For native Chip select]

We cannot set pins correctly.

Please see above comment. "Mar 25, 2016 11:04 AM"

Could you give me some advice?

[For glitch with CS-GPIO]

The glitch timing is random.

And there is the case that glitch width is increased.

In this case, CS becomes active during glitch of the clock.

As a result, eCSPI reads unpredictable value.

Is there the method to make a clock line High forcibly?

Please see waveform of the increased glitch width.

The attached file is ECSPI_glitch_on_clock.xlsx.

Is it effective that a dummy reed is put when SS is switched?

Could you give me some advice?

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuuki,

From what I have seen in the code I made a mistke, it seems that the SPI driver is expecting the SS pins to be configured as GPIO. I am trying to figure out if the driver itself is the one that modifies the SS line or maybe other process.

Is that gpio used or referenced in other device nodes? If you are able to send a way to reproduce the problem in one of our boards please share it. Have you checked that if you use a different gpio you get the same behavior?

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alejandrolozano-san,

Thank you for your support.

> Is that gpio used or referenced in other device nodes?

=>

No.

This pin is not used or referenced in other Device nodes.

> If you are able to send a way to reproduce the problem in one of our boards please share it.

=>

In SABRE board, one device is only connected to SPI port.

Therefore we cannot reproduce a problem with an SABRE board.

> Have you checked that if you use a different gpio you get the same behavior?

=>

We will consider it.

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuuki,

I have tried with the sabre-ai, I know the derivative is different but the ECSPI module is the same and I have not been able to reproduce the error. I just contacted the experts for help. Let me see if I am able to reproduce the error in a bareboard project. That will help to identify if it is a wrong configuration or a silicon problem.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share the dts and dtsi files and the steps and commands you perform to reproduce the problem?

Best Regards,

/Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alejandro-san,

We have an additional question.

(1)

Does BSP include a cord to use SS of the hardware?

(2)

When SCKL_POL was set, is there the prescribed max time when the setting is reflected to a real waveform?

There is a patch to add a delay from SCKL_POL setting to XCH bit setting.

Would you tell me the reason why this patch is necessary?

Your prompt reply would be appreciated

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuuki,

Sorry if this is taking too long, but on my side is difficult to reproduce the error due the lack of the correct hardware.

I have contacted the experts so they can shed some light on this. I will get back to you as soon as I get something useful.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alejandro-san,

Sorry for pushing you, how about the situation afterward?

Please advise of your findings.

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sabre-ai uses ECSPI1 and SS1 for the SPI NOR. Let me check if I am able to reproduce the error on that board.

I will get back to you as soon as possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alejandrolozano-san,

Thank you for your support.

We tried to enable the native Chip select of the ECSPI module.

However, each pin was not changed to the SS signal.

If there is the setting that we overlook, would you tell me?

<set Registers>

- IOMUXC_SW_MUX_CTL_PAD_EIM_EB2_B

set value : 0x1(MUX_MODE:ECSPI1_SS0)

actual value : 0x5(MUX_MODE:GPIO2_IO30)

- IOMUXC_SW_MUX_CTL_PAD_KEY_COL2

set value : 0x0(MUX_MODE:ECSPI1_SS1)

actual value : 0x5(MUX_MODE:GPIO4_IO10)

- IOMUXC_SW_MUX_CTL_PAD_KEY_ROW2

set value : 0x0(MUX_MODE:ECSPI1_SS2)

actual value : 0x5(MUX_MODE:GPIO4_IO11)

We set the following in dtsi file.

[Setting in dtsi file]

============================================

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

hog {

pinctrl_hog_1: hoggrp-1 {

fsl,pins = <

MX6QDL_PAD_EIM_EB2__ECSPI1_SS0 0x000170B0 /* out ECSPI1 SS0 */

MX6QDL_PAD_KEY_COL2__ECSPI1_SS1 0x000170B0 /* out ECSPI1 SS1 */

MX6QDL_PAD_KEY_ROW2__ECSPI1_SS2 0x0001A0B0 /* out ECSPI1 SS2 */

============================================

ecspi1 {

pinctrl_ecspi1: ecspi1_grp-1 {

fsl,pins = <

MX6QDL_PAD_EIM_D16__ECSPI1_SCLK 0x0001A0B0

MX6QDL_PAD_EIM_D18__ECSPI1_MOSI 0x0001A0B0

MX6QDL_PAD_EIM_D17__ECSPI1_MISO 0x0001A0B0

MX6QDL_PAD_EIM_EB2__ECSPI1_SS0 0x000170B0

MX6QDL_PAD_KEY_COL2__ECSPI1_SS1 0x000170B0

MX6QDL_PAD_KEY_ROW2__ECSPI1_SS2 0x0001A0B0

>;

};

============================================

&ecspi1 {

fsl,spi-num-chipselects = <3>;

cs-gpios = <0>,<0>,<0>; /* active level select is DON'T-CARE here */

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi1>;

status = "okay";

============================================

Could you give me some advice?

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alejandro-san,

Thank you for your support.

We will confirm these contents.

About glitch in CS-GPIO, we attach our source code.

Would you check it?

If this is no good cord, please point it out.

The SABRE-SD board uses only eCSPI1_SS0.

Therefore we think that it cannot be checked with SABRE-SD board.

Best Regards,

Yuuki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alejandro-san,

Thank you for your support.

In NXP Linux BSP, GPIO controls an SS signal.

This GPIO (SS signal) does not synchronize with a clock.

An SS signal may be asserted before this glitch occurs.

In this case, unpredictable data is read.

We do not know why glitch of the clock occurs.

We are looking for a method avoiding this glitch.

Best Regards,

Yuuki