As the title,

the camera inputs to MIPI-CSI.

Then, MIPI-CSI converts the data to the parallel CSI.

So, my question is, is the MIPI-CSI pixel clock limit the same as the CSI block limitation, 80MHz?

Or, can I input the 1080p camera? the pixel clock is about 125MHz.

Thanks.

已解决! 转到解答。

Hi @Hamish1 ,

The csi pixel clock is limit to 80M. The mipi-csi input data rate must under this limit.

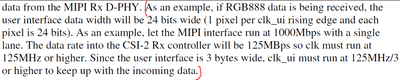

about the relation of the CSI_UI clock, there is a discription from our RM:

according to the MIPI interface freq, we can calculate the UI_clk, by:

ui_clk = MIPI_interface * datalanes / data-wide, where the MIPI_interface is 1.2/1.5Gbps, the datalanes is 2, and the data-wide is 24 for rgb888, or 16 for rgb565 from camera; so the ui_clk is 1.5G * 2 / 24(rgb888 as an example) = 125MHz, so we need to configure the ui_clk as 125MHz, then can capture the coming data. But please not that, the csi model can not support up to 125MHz pixel clk.

that means, for the rgb888, and 1.5G MIPI interface input, 2 lanes, RT1170 can not hold.

Regards,

Jing

Hi @Hamish1 ,

The csi pixel clock is limit to 80M. The mipi-csi input data rate must under this limit.

about the relation of the CSI_UI clock, there is a discription from our RM:

according to the MIPI interface freq, we can calculate the UI_clk, by:

ui_clk = MIPI_interface * datalanes / data-wide, where the MIPI_interface is 1.2/1.5Gbps, the datalanes is 2, and the data-wide is 24 for rgb888, or 16 for rgb565 from camera; so the ui_clk is 1.5G * 2 / 24(rgb888 as an example) = 125MHz, so we need to configure the ui_clk as 125MHz, then can capture the coming data. But please not that, the csi model can not support up to 125MHz pixel clk.

that means, for the rgb888, and 1.5G MIPI interface input, 2 lanes, RT1170 can not hold.

Regards,

Jing