- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- RT1052 1V2 rail

RT1052 1V2 rail

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am bring up a custom PCB and the SNVS, DCDC and 3V3 rails all come up OK in the right order. As a result I was expecting the 1V2 rail to come up to power the M7 core, but it doesn't. I have the inductor and caps connected right but nothing. Is there anything I have to do to enable it?

Thanks

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

UPDATE: I populated another PCB and all the rails come up OK now. I guess I can put this one down to manufacturing issues?

Thanks for the advise

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

UPDATE: I populated another PCB and all the rails come up OK now. I guess I can put this one down to manufacturing issues?

Thanks for the advise

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin

one can check design, also paying attention to clocks, using

sect.3. Power supply, sect.4. Clocks

Hardware Development Guide for the MIMXRT1050 Processor

https://www.nxp.com/docs/en/user-guide/MIMXRT1050HDUG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, thanks for your help.

I've been looking at it this morning. The SNVS rail (3V3) comes up first, along with the DCDC rail (3V). I can see the DCDC start to come up (PSWITCH is high around 1ms after DCDC). The 1V2 rail (VDD_SOC_IN, aka the output from the internal DCDC) rises to around 1V then gets very noisy. At this point the DCDC rail dips and the 1V2 rail collapses.

I have had a good look through the Hardware Development Guide for the MIMXRT1050 Processor and can't see what i'm doing wrong.

The DCDC rail just goes to balls L1, L2 and K4, and the 1V2 rail coming out of the inductor / Cap filter just goes to the VDD_SOC_IN balls and the DCDC_SENSE ball (J5). I have all the required caps fitted around the RT1052.

I am using rev B silicon if that makes any difference?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

so do you have working clocks in XTALI/XTALO, RTC_XTALI/RTC_XTALO,

may be useful to look at Figure 45-1. Power system overview i.MX RT1050 Processor Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMXRT1050RM.pdf

sect.4.2.2 Integrated LDO voltage regulator parameters, sect.4.2.4 On-chip oscillators

i.MXRT1050 Datasheet

https://www.nxp.com/docs/en/data-sheet/IMXRT1050CEC.pdf

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No the clocks are not working - but I think this is because they are powered from VDD_SOC_IN? I don't have an RTC clock fitted anyway.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

according to sect.4.2.4.2 OSC32K - it is powered from VDD_SNVS_IN.

from sect.4.2.4.1 OSC24M - it is powered from NVCC_PLL.

from Figure 45-1 - NVCC_PLL produced from NVDD_HIGH_IN through LDO_1P1.

So seems they all should work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OSC32K appears to be the RTC - which I am not using (N9 tied to GND and P9 floating)

NVCC_PLL is connected to ball P10 (from Table 81) - which I can check and confirm has 1.1V on it. But VDD_HIGH_IN is powered up after DCDC so shouldn't be interfering with VDD_SOC_IN should it?

I will try to get the 24MHz clock working in the meantime

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Update: Using the Eval PCB (MIMXRT1050-EVK) I have been testing the clock and VDD_SOC_IN rail.

1. I can see that the VDD_SOC_IN comes up around 270ms before the 24 MHz xtal starts oscillating

2. If I remove J36 to stop the VDD_SOC_IN rail from coming up the 24 MHZ xtal never starts ups. I can see repeated attempts about every 270ms where it tries to start but fails.

On my PCB the XTAL never even tries to start.

So the DCDC seems to be able to interfere with the XTAL operation, even though it doesn't power it directly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

NVCC_PLL does not depend on VDD_SOC_IN rail, it is produced from VDD_HIGH_IN.

Do you have VDD_HIGH_IN, VDD_HIGH_CAP, NVCC_PLL powered ?

For dcdc one also can look at AN12146 Table 2 "Power", notes for DCDC_PSWITCH

https://www.nxp.com/docs/en/nxp/application-notes/AN12146.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes VDD_HIGH_IN, VDD_HIGH_CAP and NVCC_PLL are all powered. I have looked at the app note and have made any adjustments but still no 24 MHz xtal output and no VDD_SOC_IN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one can check PMIC_ON_REQ, as described in sect.20.5.1 Turn on DCDC i.MXRT1050 RM:

To turn on the DCDC, PSWITCH and PMIC_ON_REQ must be both high

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

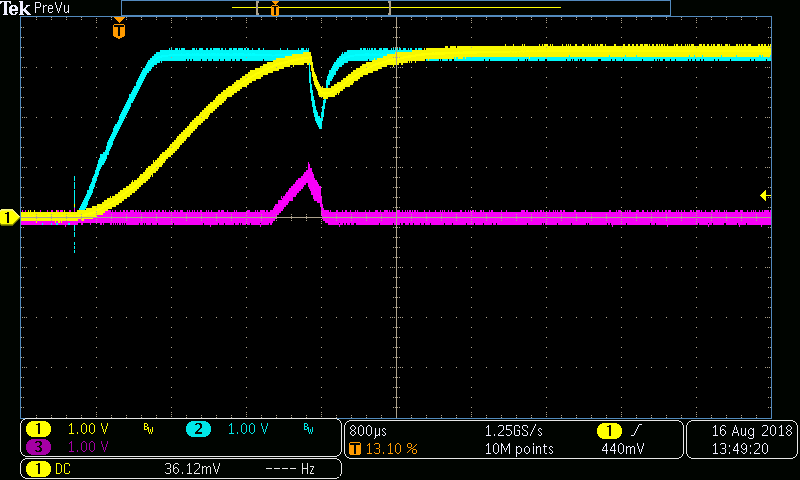

Yes I can see that they are both high (3.3 volts). In the screenshot below the blue trace is the VDD_HIGH, VDDA_ADC_3P3, and DCDC rails (they are all joined together, the SNVS comes up 250 ms before). The yellow trace is the PSWITCH and the purple trace is the VDD_SOC_IN (1V2 rail). PMIC_ON_REQ is connected to the enable line of the DCDC reg so comes up just before the DCDC rail.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

actually in the screenshot above the blue trace is sagging below 2V which violates power-up sequence and

voltage levels for VDD_HIGH, DCDC rails (min. about 2.8-3.0V depending on chip revision).

They should be smooth and its levels comply with Table 9. Operating ranges i.MX RT1050 Datasheet

https://www.nxp.com/docs/en/data-sheet/IMXRT1050CEC.pdf

Reason for voltages sagging may be layout errors (short circuits, broken traces), too big capacitors

(check sect.7.2. Placement of bulk and decoupling capacitors Hardware Development Guide

for the MIMXRT1050 Processor), insufficient power supply current which feeds processor.