- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: How to reconfigure the flexRAM on i.mxRT 1062 using MCUXpresso

How to reconfigure the flexRAM on i.mxRT 1062 using MCUXpresso

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to reconfigure the flexRAM on i.mxRT 1062 using MCUXpresso

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to double the DTCM from the default 125K to 256K without Fusing the configuration value. From the Application note AN12077, I understand that it can be done using FLEXRAM_BANK_CFG defined in IOMUXC_GPR_GPR17.

After a quick search in NXP community I found a thread on FlexRAM and Linker Problem. I followed the solution provided by Jack King to change the Stack to the start of RAM and added the IOMUXC_GPR_GPR17 update at the beginning of ResetISR function. This resolves the problem of the Debugger hanging, but malloc is failing (hardfault) in RTOS based examples. Could you please let me know what is missing in my case.

We have a custom board with i.mxRT1062, where the issue originated. But I can reproduce it on a RT1060 eval board too.

Thanks & Regards,

Rajani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @victorjimenez , @rajani_kolani

Sorry for my disturb.

I have the same issue when reallocate FlexRAM on RT1064.

I am using IAREW, so I setting FlexRAM in startup_MIMXRT1064.s as below.

__iomux_gpr14_adr EQU 0x400AC038

__iomux_gpr16_adr EQU 0x400AC040

__iomux_gpr17_adr EQU 0x400AC044

__flexram_bank_cfg EQU 0x55555555 ; 512k OCRAM, 0k DTCM, 0k ITCM

__flexram_itcm_size EQU 0x0 ; 0K

__flexram_dtcm_size EQU 0x0 ; 0K

;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

;;

;; Default interrupt handlers.

;;

THUMB

PUBWEAK Reset_Handler

SECTION .text:CODE:REORDER:NOROOT(2)

Reset_Handler

CPSID I ; Mask interrupts

LDR R0, =0xE000ED08

LDR R1, =__vector_table

STR R1, [R0]

LDR R2, [R1]

MSR MSP, R2

; NOTE: FLEXRAM_CFG_ENABLE

DSB

ISB

LDR R0,=__iomux_gpr17_adr ; load IOMUXC_GPR17 register address to R0

MOV32 R1,__flexram_bank_cfg ; move FlexRAM configuration value to R1

STR R1,[R0]

DSB

ISB

LDR R0,=__iomux_gpr16_adr ; load IOMUXC_GPR16 register address to R0

LDR R1,[R0] ; load IOMUXC_GPR16 register value to R1

ORR R1, R1, #4 ; set corresponding FLEXRAM_BANK_CFG_SEL bit

STR R1,[R0] ; store the value to IOMUXC_GPR16 (user defined FlexRAM cfg enabled)

DSB

ISB

; NOTE: FLEXRAM_ITCM_ZERO_SIZE

LDR R0,=__iomux_gpr16_adr ; load IOMUXC_GPR16 register address to R0

LDR R1,[R0] ; load IOMUXC_GPR16 register value to R1

AND R1, R1, #0xFFFFFFFE ; clear corresponding INIT_ITCM_EN bit

STR R1,[R0] ; store the value to IOMUXC_GPR16 (disable ITCM)

DSB

ISB

; NOTE: FLEXRAM_DTCM_ZERO_SIZE

LDR R0,=__iomux_gpr16_adr ; load IOMUXC_GPR16 register address to R0

LDR R1,[R0] ; load IOMUXC_GPR16 register value to R1

AND R1, R1, #0xFFFFFFFD ; clear corresponding INIT_DTCM_EN bit

STR R1,[R0] ; store the value to IOMUXC_GPR16 (disable DTCM)

DSB

ISB

; NOTE: FLEXRAM_XTCM_POWER_OF_TWO_SIZE

LDR R0,=__iomux_gpr14_adr ; load IOMUXC_GPR14 register address to R0

LDR R1,[R0] ; load IOMUXC_GPR14 register value to R1

MOVT R1, #0x0000 ; clear upper halfword of IOMUXC_GPR14 register

MOV R2, #__flexram_itcm_size

MOV R3, #__flexram_dtcm_size

LSL R2, R2, #16

LSL R3, R3, #20

ORR R1, R2, R3

STR R1,[R0] ; store the value to IOMUXC_GPR14

DSB

ISB

LDR R0, =SystemInit

BLX R0

CPSIE I ; Unmask interrupts

LDR R0, =__iar_program_start

BX R0

And I set RAM in .icf file from 0x20200000~ 0x202FFFFF

As your above discussions, must change RAM setting in BOARD_ConfigMPU() as below, but I can't find where 0K (ARM_MPU_REGION_SIZE_0KB) is defined in mpu_armv7.h

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_0KB ???);

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_0KB ???);

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);

/* Region 8 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(8, 0x20280000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);

By the way, If I want to set FlexRAM to (320k OCRAM, 128k DTCM, 64k ITCM ), how to I set size for OCRAM with 320K?

In mpu_armv7.h, 320K is not defined too.

I think It will be liked this, is it right?

/* Region 8 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(8, 0x20280000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB | ARM_MPU_REGION_SIZE_64KB);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Rajani,

Could you please share with me the community thread from Jack King that you referred to?

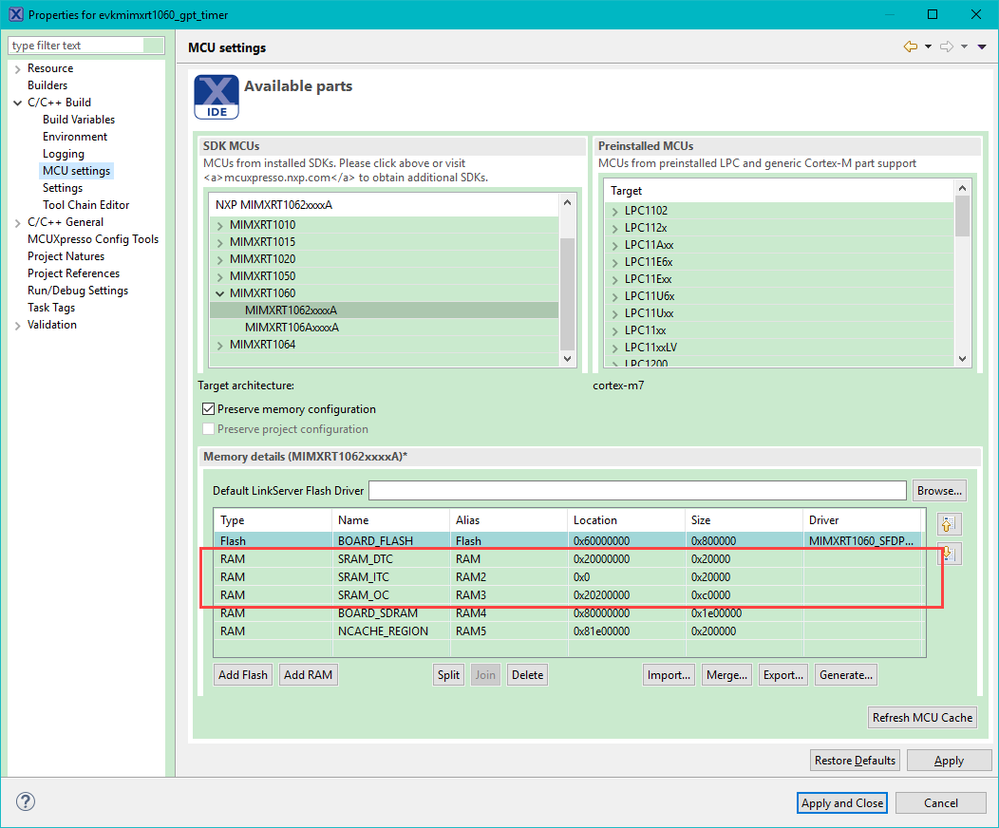

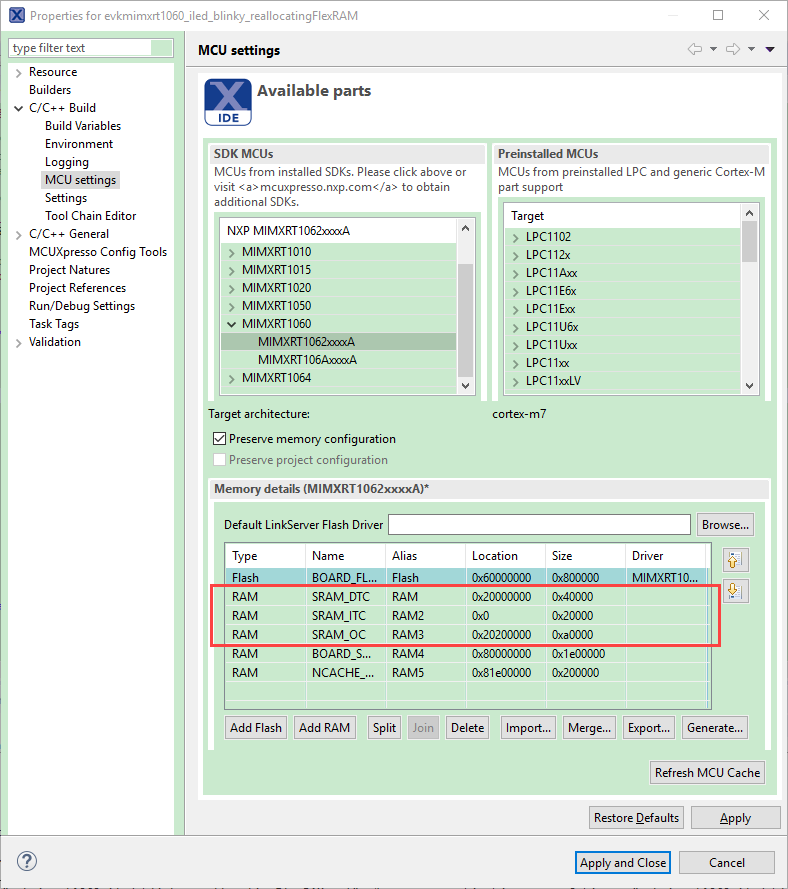

Besides changing the IOMUXC_GPR_GPR17 register during the startup you also need to modify the MCU settings so the new FlexRAM sizes match the ones that you are configuring on the register IOMUXC_GPR_GPR17.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Victor,

The link to the thread I followed is given below

https://community.nxp.com/message/1305829?commentID=1305829&et=watches.email.thread

The solution was provided by Jack King as below

It is for imxRT1052, but I thought I could do the same for imxRT1062.

Fundamentally I need to increase the DTC RAM to 256K. Could you please let me know how to do this?

Thanks & Regards,

Rajani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajani,

First, it's important to mention that the reallocating of the FlexRAM has to be done before you initialize the FlexRAM. So, reallocating the FlexRAM has to be done at the begging of the ResetISR that is located in the file startup_mimxrt1062.c. The following code reallocates the FlexRAM in the following way: DTC = 265KB, ITC = 128KB and OC = 640KB

__asm (".syntax unified\n"

"LDR R0, =0x400ac044\n"

"LDR R1, =0x55ffaaaa\n"//FlexRAM configuration DTC = 265KB, ITC = 128KB, OC = 640KB

"STR R1,[R0]\n"

"LDR R0,=0x400ac040\n"

"LDR R1,=0x04\n"

"LDR R3,[R0]\n"

"ORR R2,R1,R3\n"

"STR R2,[R0]\n"

".syntax divided\n");

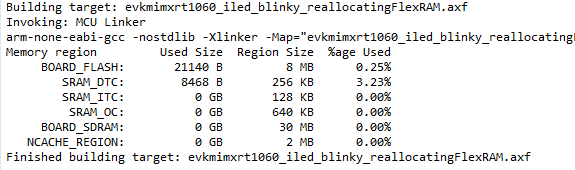

Once you added this code on the ResetISR you need to modify the memory details of the project to match this new configuration. This can be done with the MCU settings of the project.

At this point, you can compile the project without any problems and in the MCUXpresso console, you will see that the changes that you just made took effect.

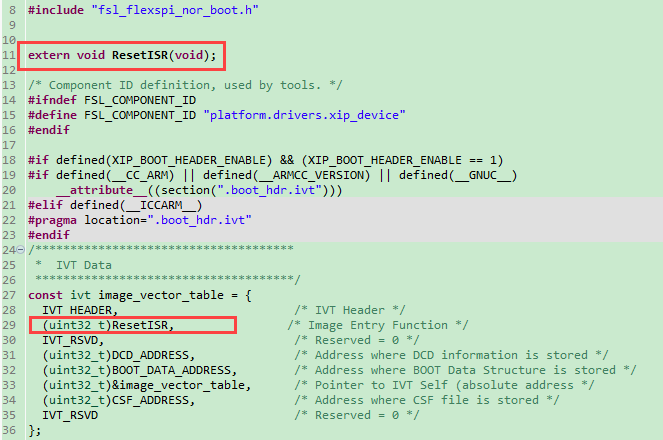

The last change that you need to make it's in the file fsl_flexspi_nor_boot.c. In this file, it's declared the image vector table which contains the image entry function. You need to change this to be the ResetISR.

That's it! Now you should be able to compile and debug the project without any problems.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Victor,

How is the value 0x55FFAAAA arrived at?

In the FlexRAM allocation application note the value for the configuration of 256k DTC 128k ITC 128k+512k OC is given as 0b01011010101011111111101010100101 which in hex is 0x5AAFFAA5.

I want to use a configuration of 448k DTC 64k OCRAM which in the application note is given as 0b10101010101010101010101010100101, how do I translate this to hex?

I'm using the i.MX RT 1050 EVKB.

Thanks,

Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good, helpful explanation. Only missing point is moving the stack, which is necessary if ResetISR() is written in C and not assembler.

One question though: why the change to fsl_flexspi_nor_boot.c? I just changed this back in my test code and it works fine as well, although I did move the stack to the beginning of DTC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Victor,

Thanks for the detailed explanation. It did fix my issue. Just one more question before closing this issue, do I need to change anything inside the void BOARD_ConfigMPU(void)

function? I remember reading somewhere that the Regions 4,5&6 need to be updated if the RAM size is adjusted!

Best Regards,

Rajani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajani,

Could you please tell me where did you read that? There's no need to modify anything related to the MPU when you reallocate the FlexRAM.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Victor,

I couldn’t locate the exact thread as I was searching generally for RAM configuration in the community! I think it may be this one

https://community.nxp.com/message/1248285?commentID=1248285#comment-1248285

it mentions -- Yes, it's also necessary to adapt the BOARD_ConfigMPU() to fit the management of the memory allocation. By jeremyzhou<https://community.nxp.com/people/jeremyzhou>.

Thanks & Regards,

Rajani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajani,

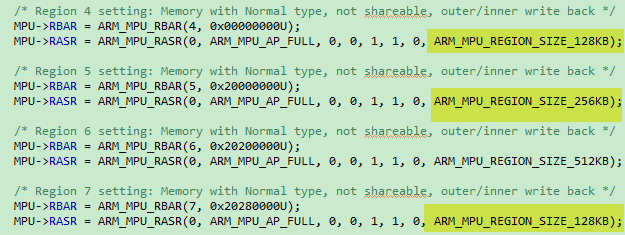

Thanks for your patience regarding this thread. I checked this with our applications team directly and you were right. When modifying the FlexRAM, you also need to change the BOARD_ConfigMPU to match these new configurations. For example, in your case that you wanted to have the following configuration: DTC = 265KB, ITC = 128KB, and OC = 640KB. You need to change Regions 4, 5, and 7 of the BOARD_ConfigMPU function to match this new configuration. So your BOARD_ConfigMPU function should look like the following:

Have a great day,

Victor

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct"button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content