- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: How to make full use of SRAM_DTC please?

How to make full use of SRAM_DTC please?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, All

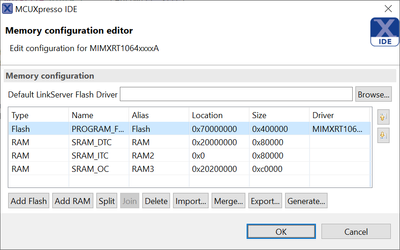

I followed this post https://community.nxp.com/t5/i-MX-RT/FlexRAM-and-Linker-Problem/m-p/990512 , specially from JackKing and intended to make full use of SRAM_DTC as below.

My usage of SRAM_DTC is about 27%, bigger than default 128K, it compiles fine,

Memory region Used Size Region Size %age Used

PROGRAM_FLASH: 208472 B 4 MB 4.97%

SRAM_DTC: 144908 B 512 KB 27.64%

SRAM_ITC: 0 GB 512 KB 0.00%

SRAM_OC: 896 B 768 KB 0.11%

but when it runs, it comes up with a hard fault.

Help, please, i need to make full use of the RAM as it is a bigger project.

Regards!

Ping

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Ping

I do it on the fly (preserving stack) but that is a special technique requiring observing additional rules (with special code to do the switch and keep the processor stack at the same address location).

Generally it needs to be done before RAM is being used for anything (no variables, no stack and not within a subroutine that needs to return). Basically it is best to do it as very first instruction executed at the reset vector to be sure that it is always safe. That is, very first thing in ResetISR() if you use SDK code.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

According to your reply, it seems that the hardfault arises immediately after entering the debug mode.

It seems a bit weird, so I was wondering if you can demonstrate the steps of reconfiguring the FlexRAM, it can help me to figure the issue out.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am looking for an simple and successful example of RAM configuration, as my project requires more DTC RAM, browsed several posts and haven't found any marked as solution. Now the project is moved to RT1024, and the RAM is even smaller there, so I urgently need to configure the useful RAM - DTC to at least 128k. Where shall I set OMUXC_GPR_GPR17 described in AN12077? and with what kind of memory configuration pls?

Regards!

Ping

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

To change FlexRAM sizes the following sequence is used:

1. Write memory type sizes (rounded up to power of two sizes)

IOMUXC_GPR_GPR14

2. Write the sector configuration (2 bits per sector defining whether off, or which RAM type it is assigned to)

IOMUXC_GPR_GPR17

3. Switch over from the setting configured by eFUSE to that configured by GPR17 by setting the FLEXRAM_BANK_CFG_SEL_CFG flag in IOMUXC_GPR_GPR16

Details are also given in the application note.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks, Mark

shall i do this first in main.c? or is it too late?

Regards!

Ping

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Ping

I do it on the fly (preserving stack) but that is a special technique requiring observing additional rules (with special code to do the switch and keep the processor stack at the same address location).

Generally it needs to be done before RAM is being used for anything (no variables, no stack and not within a subroutine that needs to return). Basically it is best to do it as very first instruction executed at the reset vector to be sure that it is always safe. That is, very first thing in ResetISR() if you use SDK code.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks, Mark

It is working!

Ping

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Changing the FlexRAM configuration moves the addressing of "all/multiple" FlexRAM sectors so generally needs to be performed before any RAM is being used (or configured via eFUSE) to avoid failure.

See chapter 11 of https://www.utasker.com/docs/iMX/i.MX_RT_1064_uTasker.pdf for more practical details about the remapping. The uTasker project supports dynamic (on-the-fly at run-time) FlexRAM remapping as detailed there but this advanced capability is not available in the SDK.

Beware that disabling OCRAM can have negative consequences for the ROM-LOADER, resulting in a board not being able to start after a software or watchdog reset. If doing this it is recommended to use an external watchdog that can power cycle the processor in the event of failure.

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Contact me by personal message or on the uTasker web site to discuss professional training, solutions to problems or rapid product development requirements

For professionals searching for faster, problem-free Kinetis and i.MX RT 10xx developments the uTasker project holds the key: https://www.utasker.com/iMX/RT1064.html