- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: About UB/LB Signals behavior when SEMC is used as SRAM-I/F

About UB/LB Signals behavior when SEMC is used as SRAM-I/F

Hi George,

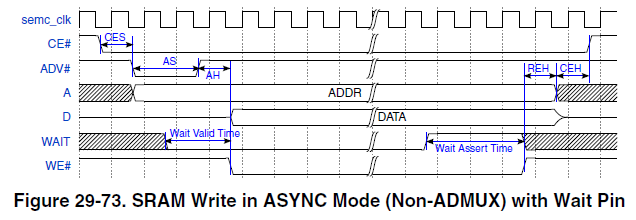

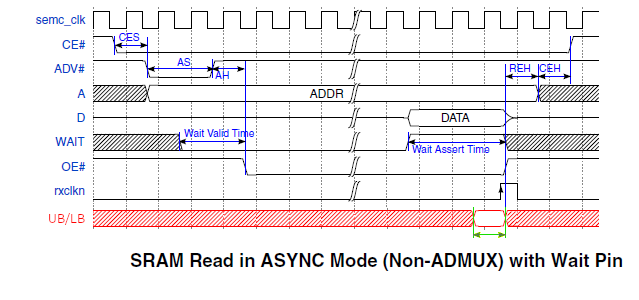

I received an update, you can take as reference see the LB#/UB# signals in ASYNC SRAM write in Non-ADMUX address mode.

Best Regards,

Felipe

Hi George,

These signals are Upper and Lower Byte select pins. SRAM will read or write upper or lower data byte depending on this signals. We do not have timing diagrams including these pins but you can find more information of this in your specific memory datasheet.

Have a great day,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored. Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

------------------------------------------------------------------------------

Dear @FelipeGarcia

The device that connects to the RT1175 is an FPGA.

We have to configure the FPGA according to the RT1175 I/F specifications.

Therefore, we need to know the cycle-based signal transition.

Other signal timings seem to be variable by the registers, but it remains unclear where the signal transitions occur for UB and LB.

For example, in the following mode :

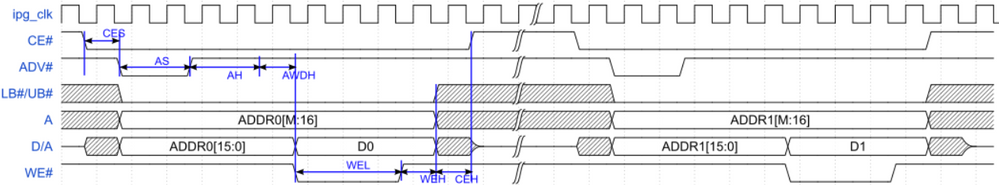

At what timing in this figure the UB and LB signals transition?

And where is it when read ?

BR,

George.

Hi George,

Unfortunately, we do not have timing diagrams including these signals. However, just for reference you can check SRAM datasheets for example: https://www.issi.com/WW/pdf/65WV25616ALL_BLL.pdf

There you will find more info about timing and behavior of these signals.

Best regards,

Felipe

Hello @FelipeGarcia

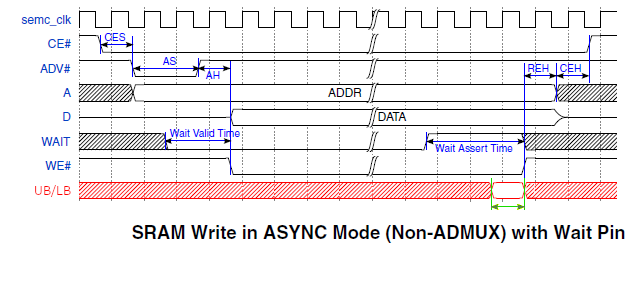

The documentation you presented to me allowed me to understand the behavior of UB/LB.

I think you can guarantee that UB / LB is valid during green period I added in red.

Is my understanding correct?

BR,

George

Hello @FelipeGarcia,

Sorry for the late reply.

The UB/LB I added may have been too extreme.

It may be necessary to extend the valid fields backward by one semc_clk.

My thoughts are as follows.

First, Write timing:

SRAM needs to capture UB/LB-gated DATA at WE# rising edge.

I think UB/LB needs setup and hold at WE# rising edge.

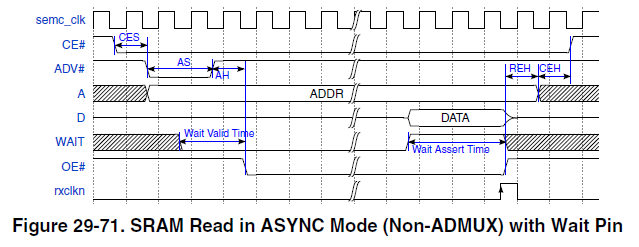

Second, Read timing:

SRAM needs to control the DATA output with UB/LB and OE, which requires setup and hold for the internal rxclkn rising edge.

Please tell me the valid period for which you can guarantee.

BR,

George