- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: ADC_ETC B2B Mode

ADC_ETC B2B Mode

Hello,

I have already posted some questions regarding ADC and ADC_ETC in this post but have got no answer so far. Now I have another question.

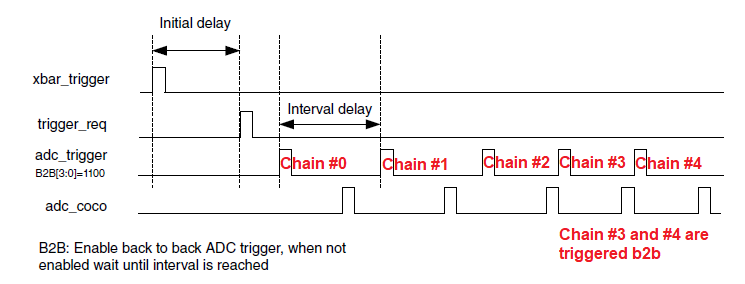

The RT1020 Reference Manual provides this diagram where I added some information for my question below.

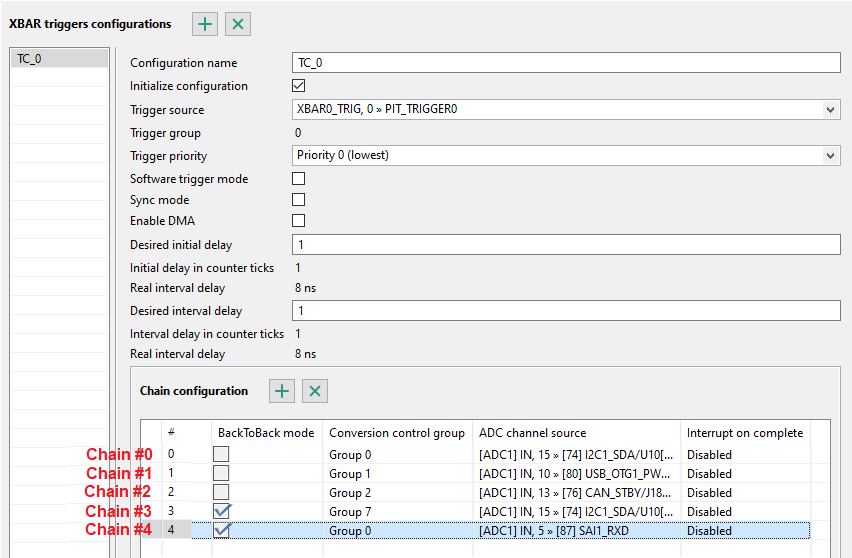

I think the above timing diagram would equal to these settings in MCUXpresso Config Tools:

*****

Question 1:

Are my following thoughts regarding the signals correct?

- The xbar_trigger comes from the peripheral I chose (PIT_TRIGGER0)

- The xbar_trigger will be internally delayed in the ADC_ETC peripheral and after the Initial delay it will generate an internal signal trigger_req.

- Some other part of the peripheral will receive the trigger_req signal and send the adc_trigger signal to the ADC peripheral. Each pulse on the adc_trigger signal corresponds to one ADC_ETC chain entry for the selected trigger. Therefore after the initial delay the first trigger pulse will start the conversion of chain element #0, the second pulse will start conversion for chain element #1 and so on. Chain elements #3 and #4 will be triggered back2back.

*****

Question 2:

Is it correct that Chain element #3 has b2b enabled which means "If chain #2 finished the conversion start conversion of chain #3 as soon as possible"?

*****

Question 3:

Is it correct that the b2b field of Chain #0 has no effect because it is the first chain # which will be triggered and it only waits for the initial delay?

****

Question 4:

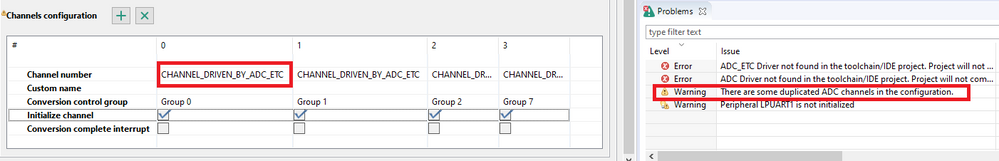

The Conversion control group can be selected for every chain element. The conversion control group specifies which control register for hardware triggers and which result register (ADCx_HCn & ADCx_Rn) will be used for the conversion.

If I set up my chain element #0 and chain element #4 to use the Conversion control group 0, will the conversion result of chain #4 overwrite the conversion result of chain #0?

****

Question 5:

Do I have to set up the Conversion control groups in the ADC peripheral driver with MCUXpresso Config Tools like this

(every Conversion control group with Channel number set to CHANNEL_DRIVEN_BY_ADC_ETC) or will it be enough to initialize the ADC_ETC and the ADC channels will be initialized by the ADC_ETC peripheral?

If I set up the channels like shown above it will result in the warning that there are some duplicated ADC channels in the configuration > the warning suggests that I am doing something wrong here.

Kind regards,

Stefan

已解决! 转到解答。

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Yes.

2) Yes.

3) Yes.

4) No, the Data in the ADCx_R0 register will be overwritten, but the data for chain elements #0 and #4 will be stored in TRIG0_RESULT_1_0 DATA0 and TRIG0_RESULT_5_4 DATA4 registers.

5) It needs to set up the conversion control groups in the ADC peripheral driver in the MCUXpresso Config Tools.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you ha

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Yes.

2) Yes.

3) Yes.

4) No, the Data in the ADCx_R0 register will be overwritten, but the data for chain elements #0 and #4 will be stored in TRIG0_RESULT_1_0 DATA0 and TRIG0_RESULT_5_4 DATA4 registers.

5) It needs to set up the conversion control groups in the ADC peripheral driver in the MCUXpresso Config Tools.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you ha