- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: opengles display incorrect on imx6q custom board

opengles display incorrect on imx6q custom board

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

opengles display incorrect on imx6q custom board

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

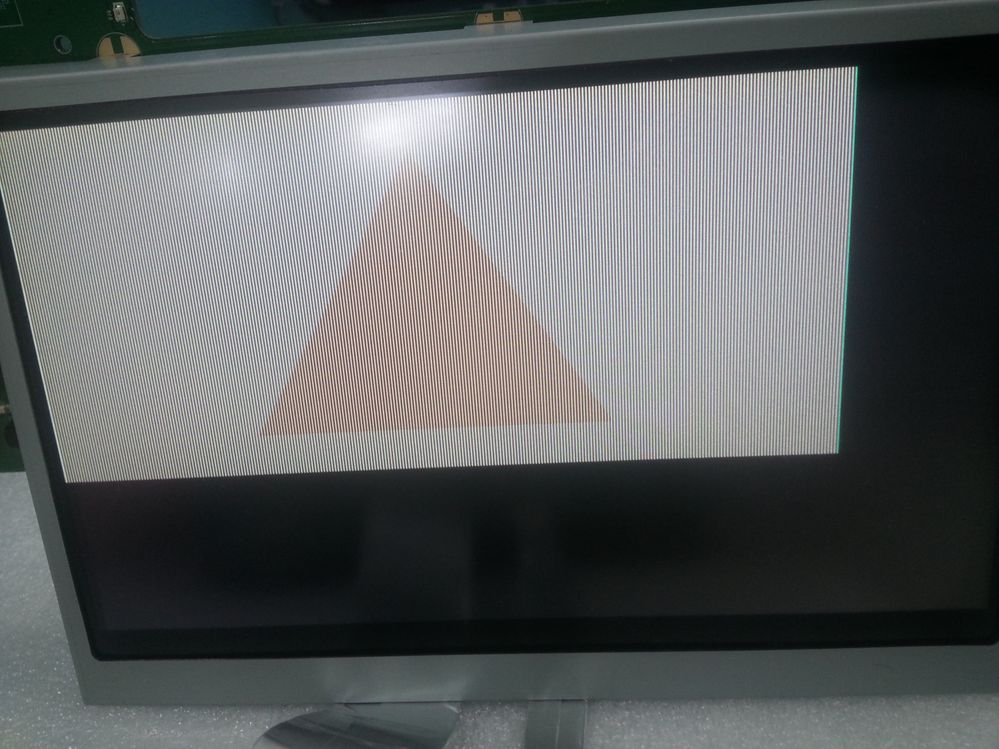

I’m porting 3.10.53 kernel to imx6qsabre based custom board, the board use rgb24 interface lcd panel,

pinctrl control config correct (u-boot logo display ok, kernel log display ok), rootfs build with yocto-layers,

but when i run a opengles 2.0 test program. it display as below, someone can give me any ideas ?

regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi zare,

Probably you need to check the uboot parameters and resolution for RGB24, also you should try the unit test for the IPU, or the OBDS.

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

thanks for you reply,

I think my resolution settings is not wrong, operating on mxcfb is ok, just opengles has problem. below is the mxcfb testing result photo. and my display pinctrl settings follow it .

my uboot pinctrl settings

#define DISPLAY_RGB_PAD_CTRL MUX_PAD_CTRL(NO_PAD_CTRL)

iomux_v3_cfg_t display_rgb_pads[] = {

MX6_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DI0_PIN15__IPU1_DI0_PIN15 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DI0_PIN2__IPU1_DI0_PIN02 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DI0_PIN3__IPU1_DI0_PIN03 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DI0_PIN4__GPIO4_IO20 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT0__IPU1_DISP0_DATA00 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT1__IPU1_DISP0_DATA01 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT2__IPU1_DISP0_DATA02 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT3__IPU1_DISP0_DATA03 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT4__IPU1_DISP0_DATA04 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT5__IPU1_DISP0_DATA05 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT6__IPU1_DISP0_DATA06 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT7__IPU1_DISP0_DATA07 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT8__IPU1_DISP0_DATA08 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT9__IPU1_DISP0_DATA09 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT10__IPU1_DISP0_DATA10 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT11__IPU1_DISP0_DATA11 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT12__IPU1_DISP0_DATA12 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT13__IPU1_DISP0_DATA13 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT14__IPU1_DISP0_DATA14 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT15__IPU1_DISP0_DATA15 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT16__IPU1_DISP0_DATA16 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT17__IPU1_DISP0_DATA17 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT18__IPU1_DISP0_DATA18 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT19__IPU1_DISP0_DATA19 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT20__IPU1_DISP0_DATA20 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT21__IPU1_DISP0_DATA21 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT22__IPU1_DISP0_DATA22 | DISPLAY_RGB_PAD_CTRL,

MX6_PAD_DISP0_DAT23__IPU1_DISP0_DATA23 | DISPLAY_RGB_PAD_CTRL

};

display parameters:

static struct display_info_t const displays[] = {{

.bus = -1,

.addr = 0,

.pixfmt = IPU_PIX_FMT_RGB24,

.detect = NULL,

.enable = NULL,

.mode = {

.name = "AA-WVGA",

.refresh = 60,

.xres = 1280,

.yres = 720,

.pixclock = 14492,

.left_margin = 107,

.right_margin = 91,

.upper_margin = 37,

.lower_margin = 11,

.hsync_len = 2,

.vsync_len = 5,

.sync = FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

.vmode = FB_VMODE_NONINTERLACED

} },

And where can i get ipu test units.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

HI,

Please try the following :

bootarg fbpix=BGR32

FYI:

Wrong Qt-Rendering with platform EGLFS

Regards,

Jayaram

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It's still not working, either I change ipu input pixel format in _setup_disp_channel1 to IPU_PIX_FMT_BGR32.

I think there is problem when gpu translate data to ipu, but I can not find where it is .

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No one can know what happened ?