- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- imx8mq stuck in uboot

imx8mq stuck in uboot

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

imx8mq

yocto

debug serial log:

U-Boot SPL 2017.03-imx_v2017.03_4.9.51_imx8m_ga+g2537522 (Mar 12 2018 - 12:25:24)

PMIC: PFUZE100 ID=0x10

start to config phy: p0=3200mts, p1=667mts with 1D2D training

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

config to do 3200 1d training.

Training PASS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

config to do 3200 2d training.

Training PASS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

pstate=1: set dfi clk done done

Training PASS

Load 201711 PIE

Normal Boot

Trying to boot from MMC1

U-Boot 2017.03-imx_v2017.03_4.9.51_imx8m_ga+g2537522 (Mar 12 2018 - 12:25:24 -0500)

CPU: Freescale i.MX8MQ rev2.0 1500 MHz (running at 1000 MHz)

CPU: Commercial temperature grade (0C to 95C) at 70C

Reset cause: POR

Model: Freescale i.MX8MQ EVK

DRAM: 3 GiB

TCPC: Vendor ID [0x1fc9], Product ID [0x5110]

MMC: FSL_SDHC: 0, FSL_SDHC: 1

*** Warning - bad CRC, using default environment

No panel detected: default to HDMI

Display: HDMI (1280x720)

debug log end =========================

imx8mq stuck in Display:HDMI(1280x720),can not run to boot kernel, when using imx-boot-imx8mqevk-sd.bin-flash_evk. But using imx-boot-imx8mqevk-sd.bin-flash_evk_no_hdmi, machine works and runs to yocto system.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeff

one can check hdmi power and clocks using i.MX8M Hardware Developer’s Guide

https://www.nxp.com/docs/en/user-guide/IMX8MDQLQHDG.pdf

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeff

for new board it is necessary to rebuild image using

guidelines provided in Chapter 4 How to bring up a new MX8M board

MX8M_DDR_Tool_User_Guide.docx included in ddr tool package

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor

Is the problem related to DDR? The difference of two version imx-boot-imx8mqevk-sd.bin just contain signed_hdmi_imx8m.bin or not.

refer to imx8mq-yocto-bsp/build-xwayland/tmp/work/imx8mqevk-poky-linux/imx-boot/0.2-r0/git/iMX8M/soc.mak:

flash_evk: $(MKIMG) signed_hdmi_imx8m.bin u-boot-spl-ddr.bin u-boot.itb

./mkimage_imx8 -fit -signed_hdmi signed_hdmi_imx8m.bin -loader u-boot-spl-ddr.bin 0x7E1000 -second_loader u-boot.itb 0x40200000 0x60000 -out $(OUTIMG)

flash_evk_no_hdmi: $(MKIMG) u-boot-spl-ddr.bin u-boot.itb

./mkimage_imx8 -fit -loader u-boot-spl-ddr.bin 0x7E1000 -second_loader u-boot.itb 0x40200000 0x60000 -out $(OUTIMG)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeff

according to suggested document, if DDR stress test passes, press ‘Gen Code’ button to

generate u-boot-spl C code Build new u-boot with the new C code files to create your board image

So for custom board imx-boot-imx8mqevk-sd.bin may not run.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeff

one can try with Demo Images

is it true (not dvi) monitor, had you tried with other hdmi panels.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor

Had tried image downloaded from link you posted, still stuck in the same place. But I find out the contrete positon where uboot stuck in.

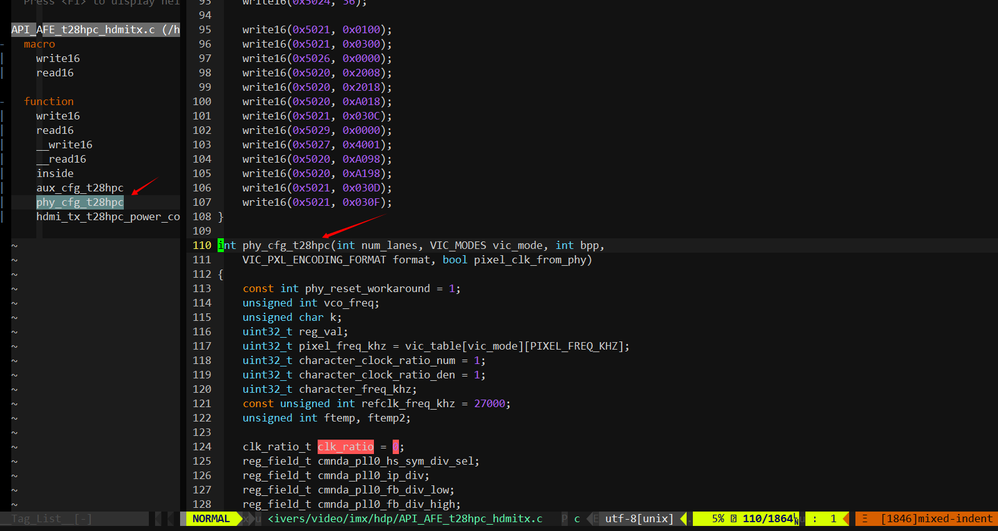

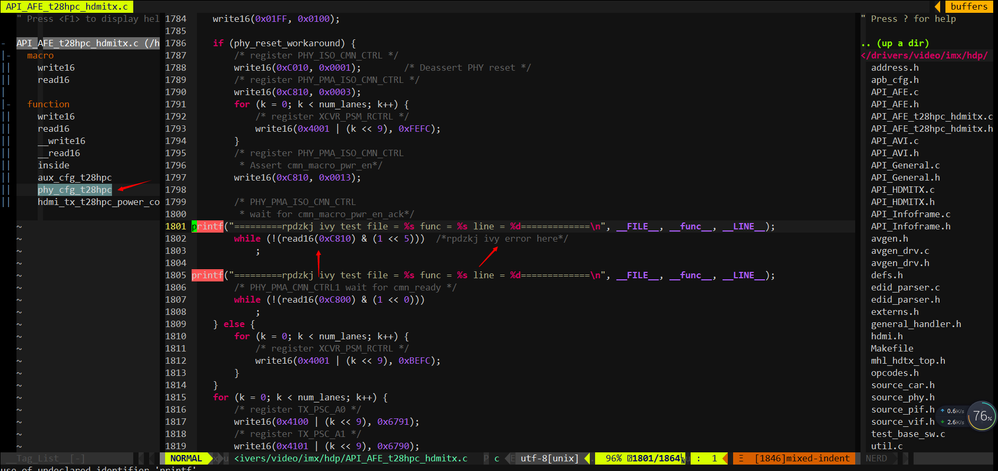

when HDMI controller init, call function phy_cfg_t28hpc from uboot/drivers/video/imx/hdp/API_AFE_t28hpc_hdmitx.c.

stuck in while (!(read16(0xC810) & (1 << 5))); about 1800 line at API_AFE_t28hpc_hdmitx.c

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeff

one can check hdmi power and clocks using i.MX8M Hardware Developer’s Guide

https://www.nxp.com/docs/en/user-guide/IMX8MDQLQHDG.pdf

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor

The reason why imx8mq stuck in uboot is missing a Crystal Oscillator of HDMI

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @ivychend

Is the 27MHz oscillator you're referring to the one that is used for HDMI PHY? Or is it the differential HDMI reference clock connected to HDMI_REFCLK_P and HDMI_REFCLK_N?

Thank you

M.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

machine runs ok serial log:

U-Boot SPL 2017.03-imx_v2017.03_4.9.51_imx8m_ga+g2537522 (Mar 12 2018 - 12:25:24)

PMIC: PFUZE100 ID=0x10

start to config phy: p0=3200mts, p1=667mts with 1D2D training

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

config to do 3200 1d training.

Training PASS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

config to do 3200 2d training.

Training PASS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

pstate=1: set dfi clk done done

Training PASS

Load 201711 PIE

Normal Boot

Trying to boot from MMC1

U-Boot 2017.03-imx_v2017.03_4.9.51_imx8m_ga+g2537522 (Mar 12 2018 - 12:25:24 -0500)

CPU: Freescale i.MX8MQ rev2.0 1500 MHz (running at 1000 MHz)

CPU: Commercial temperature grade (0C to 95C) at 62C

Reset cause: POR

Model: Freescale i.MX8MQ EVK

DRAM: 3 GiB

TCPC: Vendor ID [0x1fc9], Product ID [0x5110]

MMC: FSL_SDHC: 0, FSL_SDHC: 1

*** Warning - bad CRC, using default environment

No panel detected: default to HDMI

Display: HDMI (1280x720)

HDMI enable failed!

In: serial

Out: serial

Err: serial

BuildInfo:

- ATF 6a83ae0

- U-Boot 2017.03-imx_v2017.03_4.9.51_imx8m_ga+g2537522

switch to partitions #0, OK

mmc0(part 0) is current device

Net:

Error: ethernet@30be0000 address not set.

No ethernet found.

Normal Boot

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc0(part 0) is current device

reading boot.scr

** Unable to read file boot.scr **

reading Image

20054528 bytes read in 450 ms (42.5 MiB/s)

Booting from mmc ...

reading fsl-imx8mq-evk.dtb

42207 bytes read in 17 ms (2.4 MiB/s)

## Flattened Device Tree blob at 43000000

Booting using the fdt blob at 0x43000000

Using Device Tree in place at 0000000043000000, end 000000004300d4de

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.9.51-imx_4.9.51_imx8m_ga+g6df7474 (bamboo@yb6) (gcc version 6.2.0 (GCC) ) #2 SMP PREEMPT Mon Mar 12 12:13:52 CDT 2018

[ 0.000000] Boot CPU: AArch64 Processor [410fd034]

[ 0.000000] earlycon: ec_imx6q0 at MMIO 0x0000000030860000 (options '115200')