- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Dear community,

We have been developing our product with iMX7D.

I am checking a Serial Audio Interface.

I hope to get a SAIx_CLK_ROOT minimum frequency value.

In the the Reference Manual IMX7DRM: Table 5-11. Clock Root Table,

it is described that the SAIx_CLK_ROOT MAX frequency value is 67.5 MHz.

But I could not find the SAIx_CLK_ROOT MIN frequency value .

[Question]

Could you tell me the SAIx_CLK_ROOT minimum frequency value ?

Best Regards,

Koichi Sakagami

已解决! 转到解答。

Hi Kochi,

In Table 5-11. Clock Root Table you can see all the available clock sources for SAI. The input with lowest frequency is 24MHz (000 - OSC_24M).

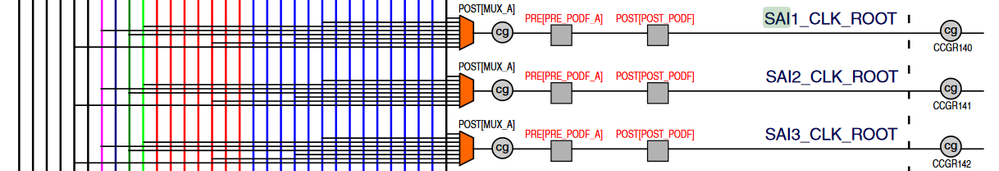

Then in Figure 5-15. CCM Clock Tree Root Slices you can find that SAIx_CLK_ROOT has a pre-divider and post-divider.

Finally in chapter 5.2.8.10 Target Register (CCM_TARGET_ROOTn) you can se that pre divider is 3 bits and post divider is 6 bits. So you can divide the 24MHz signal by 8 and then by 64 which is 45kHz approximately.

Regards,

Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Kochi,

In Table 5-11. Clock Root Table you can see all the available clock sources for SAI. The input with lowest frequency is 24MHz (000 - OSC_24M).

Then in Figure 5-15. CCM Clock Tree Root Slices you can find that SAIx_CLK_ROOT has a pre-divider and post-divider.

Finally in chapter 5.2.8.10 Target Register (CCM_TARGET_ROOTn) you can se that pre divider is 3 bits and post divider is 6 bits. So you can divide the 24MHz signal by 8 and then by 64 which is 45kHz approximately.

Regards,

Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------