- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hi,

We are doing a iMX6 design, where we want to control boot device by setting the boot config through the GPIO pins.

We are booting only from a SPI NOR flash memory.

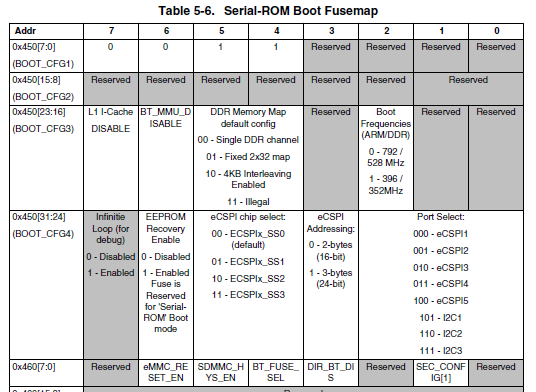

Looking at the fuse map (see figure below) there are signals/bits that are "reserved".

Does this mean that the state (high or low) of this pin at boot time is "don't care"??

I want to leave out the resistors pulling the "reserved" config bits either high or low, to keep BOM count low.

Best Regards,

Martin Christiansen.

已解决! 转到解答。

1.

As for “How long is the window where the iMX6 "reads" these config pins??” :

The boot pins are latched at POR rising edge, but - strictly speaking -

the hold time is not specified. Please look at sheet 13 of the i.MX6 SL EVK

design, where bus isolation buffer is applied and the next note is provided :

"i.MX6SL reads values approximately 300uS to 1mS after reset released.

Buffers are active while unit is in reset and 1ms-10ms after reset is released."

2.

> What are the "reserved" pins for??

As usually – for possible future options.

Regards,

Yuri.

You may use pulling up or down of the “reserved” boot pins, but please do not

leave them free. For more details, please refer to

https://community.freescale.com/thread/358921

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Yuri,

Thanks,

I can see from the post you link too, that it is not completely clear why/how to tie those pins.

How long is the window where the iMX6 "reads" these config pins??

What are the "reserved" pins for??

Thanks,

Martin.

1.

As for “How long is the window where the iMX6 "reads" these config pins??” :

The boot pins are latched at POR rising edge, but - strictly speaking -

the hold time is not specified. Please look at sheet 13 of the i.MX6 SL EVK

design, where bus isolation buffer is applied and the next note is provided :

"i.MX6SL reads values approximately 300uS to 1mS after reset released.

Buffers are active while unit is in reset and 1ms-10ms after reset is released."

2.

> What are the "reserved" pins for??

As usually – for possible future options.

Regards,

Yuri.