- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: i.MXQXP/i.MX8X Parallel CSI / Parallel Capture for a 8-bit parallel input

i.MXQXP/i.MX8X Parallel CSI / Parallel Capture for a 8-bit parallel input

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

i.MXQXP/i.MX8X Parallel CSI / Parallel Capture for a 8-bit parallel input

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

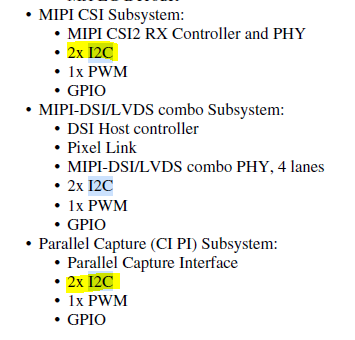

Can the i.MXQXP/i.MX8X Parallel CSI interface be used to capture low-speed, basic 8-bit data?

Looking at possibly using it for an additional 8-bit ADC with one clock.

So 1 clock input, 8 data bits, transfer per clock period.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

sorry, I thought of imx8qm, for imx8qxp parallel csi port, you can refer to the dtsi file for clock settings

ov5640: ov5640@3c {

compatible = "ovti,ov5640";

reg = <0x3c>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_parallel_csi>;

clocks = <&pi0_misc_lpcg 0>;

assigned-clocks = <&pi0_misc_lpcg 0>;

assigned-clock-rates = <24000000>;

clock-names = "xclk";

powerdown-gpios = <&lsio_gpio3 2 GPIO_ACTIVE_HIGH>;

reset-gpios = <&lsio_gpio3 3 GPIO_ACTIVE_LOW>;

csi_id = <0>;

mclk = <24000000>;

mclk_source = <0>;

status = "okay";

for this clock, you can refer to the:

pi0_misc_lpcg: clock-controller@5826301c {

compatible = "fsl,imx8qxp-lpcg";

reg = <0x5826301c 0x4>;

#clock-cells = <1>;

clocks = <&clk IMX_SC_R_PI_0 IMX_SC_PM_CLK_MISC0>;

bit-offset = <0>;

clock-output-names = "pi0_lpcg_misc_clk";

power-domains = <&pd IMX_SC_R_ISI_CH0>;

};

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, the port I have available is the Mipi CSI port. CSI_DO0 through CSI_DS07, plus Hsync and Vsync.

Would it be possible these just these pins?

Also, where can I find more details on the PI capture besides the reference manual or datasheet?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

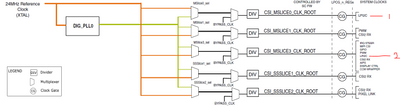

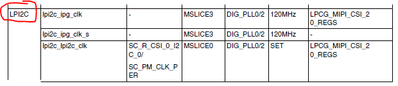

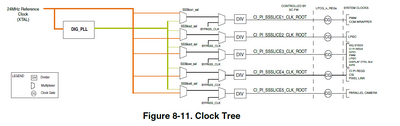

On MIPI_CSI0_I2C0_SCL and MIPI_CSI0_I2C0_SDA, there appears to be two clock paths,

But, are both the CI_PI i2c and CSI0 i2c available?

Assuming only CSI0 i2c is available, which one do these correspond? #1 or #2?

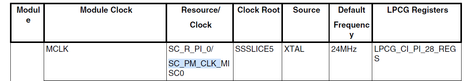

is there a choice between the 24 MHz clock and DIG_PLL0? Or is it that only the CI_PI has access to it and the CSI0 only has access to the PLL:

So, to access only the CSI0 I2C0, how many clocks enables are needed in total? Assuming that the only option is via the PLL, I just need to make sure I am only turning on what is needed, nothing more, but it seems the PLL would also has gated further upstream, or no? Or is it fixed at 120 MHz as the clock input to this CSI0 I2C0, LPI2C module?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

where did you get this picture, refer to the imx8qxp reference manual, I found a bit different

refer to the dts file

clocks = <&clk IMX_SC_R_PI_0 IMX_SC_PM_CLK_MISC0>;

for clock settings, you also can refer to the clock driver

"https://source.codeaurora.org/external/imx/linux-imx/tree/drivers/clk/imx?h=lf-5.15.y"

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Also, at what stage in boot-up does the CSI0 i2c become available? In other words, is it available prior to the application image being launched?