- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX8MM MIPI CSI: can't read RX_FIFO register from CPU

i.MX8MM MIPI CSI: can't read RX_FIFO register from CPU

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX8MM MIPI CSI: can't read RX_FIFO register from CPU

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For debugging purpose, we are trying to read the CSI RXFIFO 'manually', from code placed in mx6c_capture.c. We know the DMA is no longer running and there is data in the RXFIFO as DDRY is set.

The problem is the calls to csi_read() at address CSI_RFIFO return the same two 32bit values (which are valid), and the DDRY flag is never reset, even though the camera is no longer sending any data. So we are not emptying the FIFO.

CSI_RFIFO = Address: 32E2_0000h base + 10h offset = 32E2_0010h.

So it looks as if CSI_RFIFO is cached, or somehow we cannot empty the FIFO from the CPU. None of which make sense, nor match the Ref Manual, page 3992.

Questions:

* Why can't we read CSI_RFIFO from CPU?

* How can we read the content of the RXFIFO from CPU?

* Is there an undocumented register to know what the FIFO level is?

We have placed the code to read in function mx6s_csi_irq_handler() at a point where we know the DMA is no longer reading from the FIFO.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Anyone there?

We are drawing a blank trying to empty the CSI RXFIFO using CPU from the csi_bridge driver. We know we are reading the correct address as the two 32-bit words we get are what we expect, but why does the FIFO not empty?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @vincentz63

Can you try below code to clear FIFO?

/* Clear RX FIFO */

cr1 = csi_read(csi_dev, CSI_CSICR1);

csi_write(csi_dev, cr1 & ~BIT_FCC, CSI_CSICR1);

cr1 = csi_read(csi_dev, CSI_CSICR1);

csi_write(csi_dev, cr1 | BIT_CLR_RXFIFO, CSI_CSICR1);- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks but I do not want to clear the FIFO, I want to read what data remains in it when the DMA halts.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Anyone out there from NXP or not? This register is documented like any other register and I can find nothing in the Ref Manual that would explain why we cannot read it or how to do so...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @vincentz63

Normally, we can dump CSI registers from Linux userspace.These registers are defined in CSI IP SPEC, not in Reference Manual.

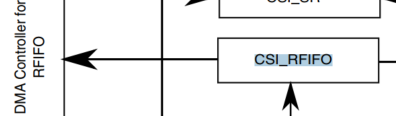

The CSI_RFIFO will only input DMA Contronller, i think you can't read FIFO if you halt DMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Qmiller,

Thanks for getting back. What is the document your refer to? I do not seem to have it, where is it?

Does it contain other registers that are not documented in the Ref Manual? Can you check if there is a RFIFO LEVEL register please?

Are you saying that only the DMA engine can read this register and that the CPU cannot?

Thanks

JP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the document your refer to? I do not seem to have it, where is it?

-->We can't send it to customer.

RFIFO LEVEL register

-->OFFSET: 8h, BIT[6:4]

000 4 Double words

001 8 Double words

010 16 Double words

011 24 Double words

100 32 Double words

101 48 Double words

110 64 Double words

111 96 Double words

Are you saying that only the DMA engine can read this register and that the CPU cannot?

-->You must read FIFO via DMA engine.CPU can't read it directly if you halt DMA. There is no direct connection between CPU and this register.