- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX6 USB-OTG Bring Up Design Verification

i.MX6 USB-OTG Bring Up Design Verification

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings,

We have a custom i.MX6Q board design and our plan is to bring the board up via serial downloader as the first option. Here I am a bit paranoid about the validity of the design so I would like to get some step-by-step confirmation on whether this will work or not?

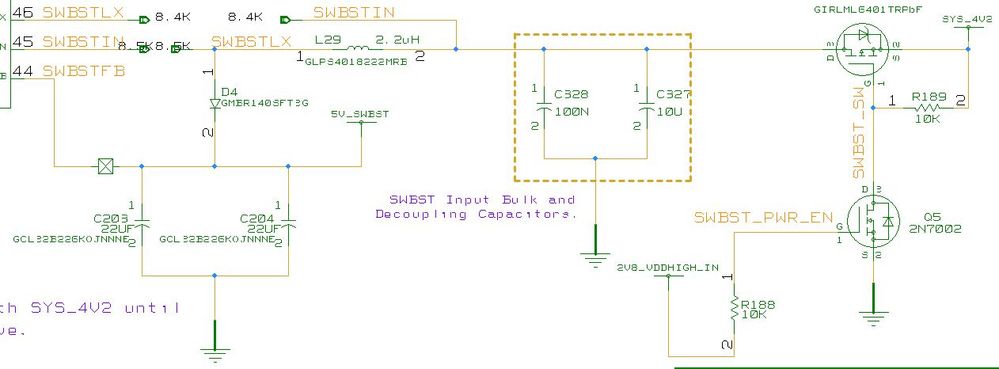

First below is the schematics to the PF0100 boost regualtor output where the USB OTG VBUS is to be powered;

I am not sure why Sabre SD followed such logic but I tried and did the same where SWBSTIN is gated by SW2 which powers the VDDHIGH rail on the processor. In Sabre SD, it is gated by AUX_3V15 but I do not believe it will make a great difference. SW2 is prior to SWBST on power-up sequence of the PMIC also.

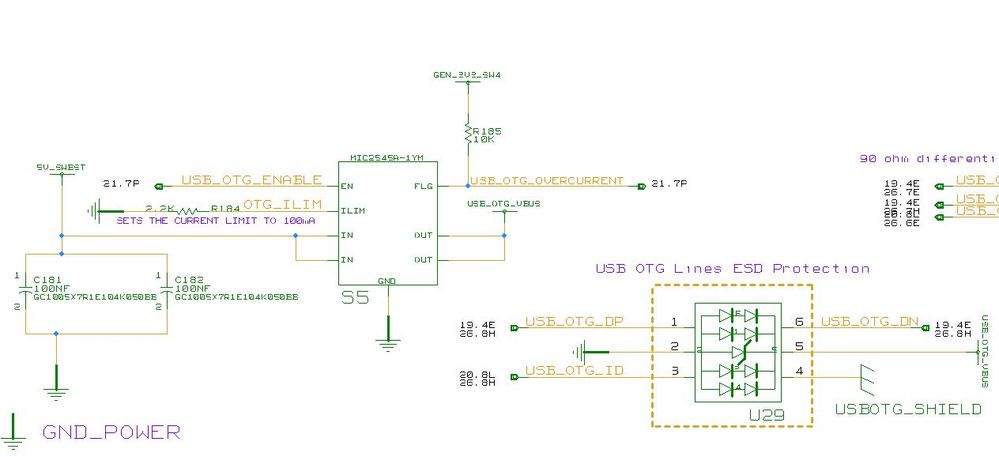

Next is the switching of the SWBST output for current limitng purposes, This is done via MIC2545A current-limit high-side switch.

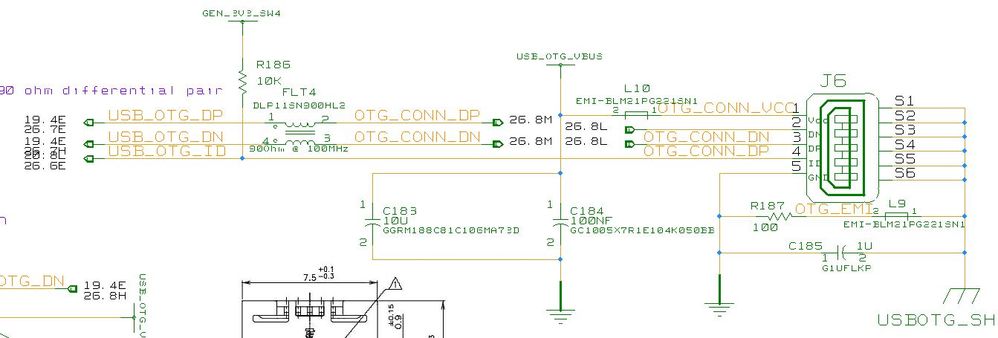

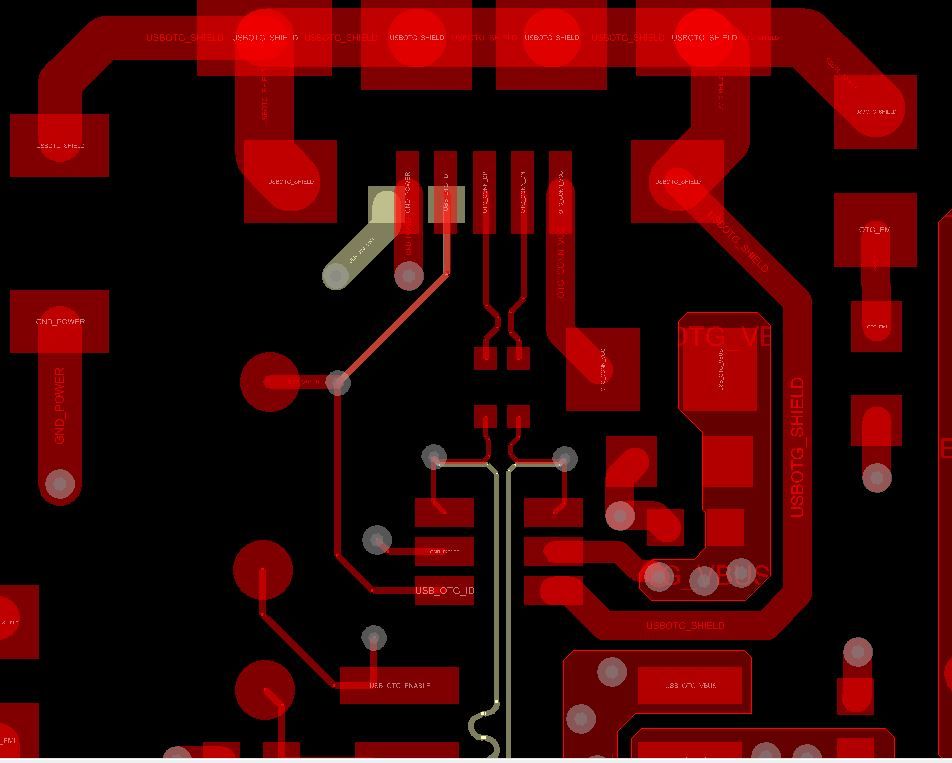

As you can see, Enable pin of the switch is not pulled high/low but connected directly to i.MX6 E23 which is the designated USB_OTG_PWR signal. SWBST output is switched here to become the USB_OTG_VBUS which is distributed to both i.MX6 OTG_VBUS and the USB connector VBUS as follows;

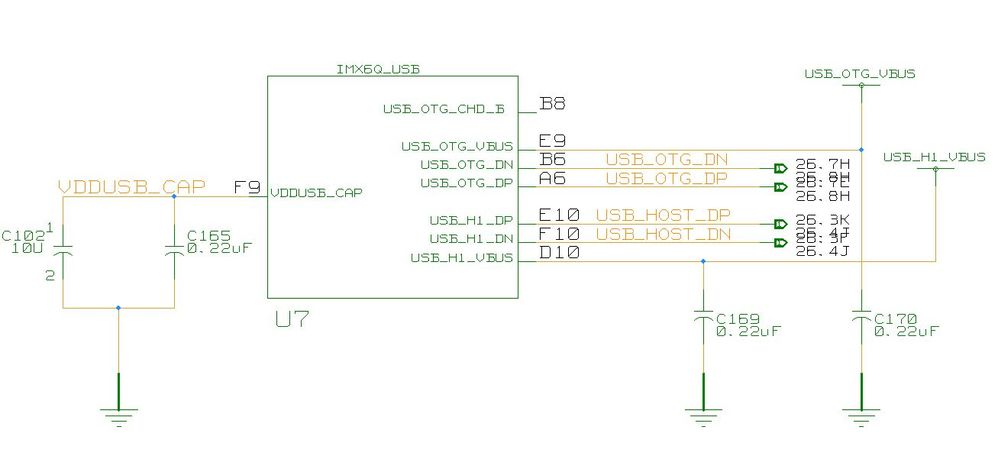

And to the i.MX6;

This is done so that the USB_OTG_VBUS is not always available but only made available when i.MX is the host. USB_OTG_ID is pulled high default at the connector input (Also there is an ESD chip there in the design in case you wonder what U29 was).

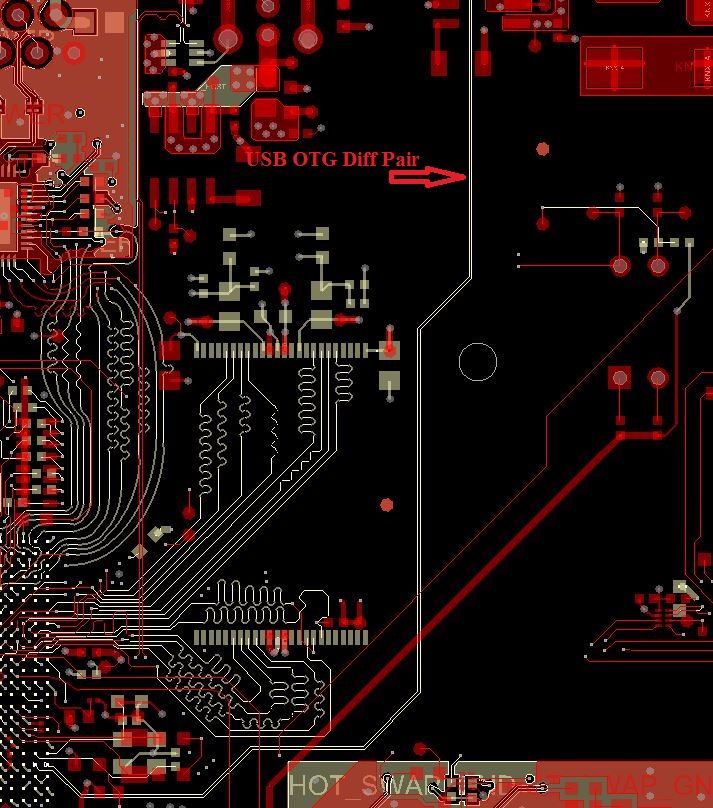

This sums up the schematic part of the design. For the layout 4 mils signals with 4 mils airgap was used to get approximately 92 ohms differential impedance and approximately 55 ohm single ended impedance. Tracks travel around 3.5 inches from the connector to the processor. From the processor to the connector the length difference between two differential signals are 0.64 mils.

At the connector vicinity;

Path from the connector to the i.MX processor;

This sums up my design. Now I wonder, when using the serial downloader to get the image into the processor, at what speed does the USB work, does it act as host or slave, who supplies the VBUS? Do you see any logic gaps in this design or errors in the layout?

If someone reading this post brought up the card using the serial downloader, please share your thoughts.

Thanks in advance,

Mete

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Everything looks OK in your design.

Q. Now I wonder, when using the serial downloader to get the image into the processor, at what speed does the USB work, does it act as host or slave, who supplies the VBUS?

A. When using the serial downloader, the i.MX6 USB OTG port operates as slave (device), VBUS is supplied by Host, the connection operates at the maximum speed the Host allows (typically, at High speed).

Q. Do you see any logic gaps in this design or errors in the layout?

A. No.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Everything looks OK in your design.

Q. Now I wonder, when using the serial downloader to get the image into the processor, at what speed does the USB work, does it act as host or slave, who supplies the VBUS?

A. When using the serial downloader, the i.MX6 USB OTG port operates as slave (device), VBUS is supplied by Host, the connection operates at the maximum speed the Host allows (typically, at High speed).

Q. Do you see any logic gaps in this design or errors in the layout?

A. No.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------