- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX6 RGMII internal reference clock 125MHz

i.MX6 RGMII internal reference clock 125MHz

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I would use the internal clock for RGMII. The external Switch have no clock reference, because the 12 wire RGMII interface dont't support that.

configuration clock: (like Hardware Development Guide)

CCM_ANALOG_PLL_ENETn - 125MHz

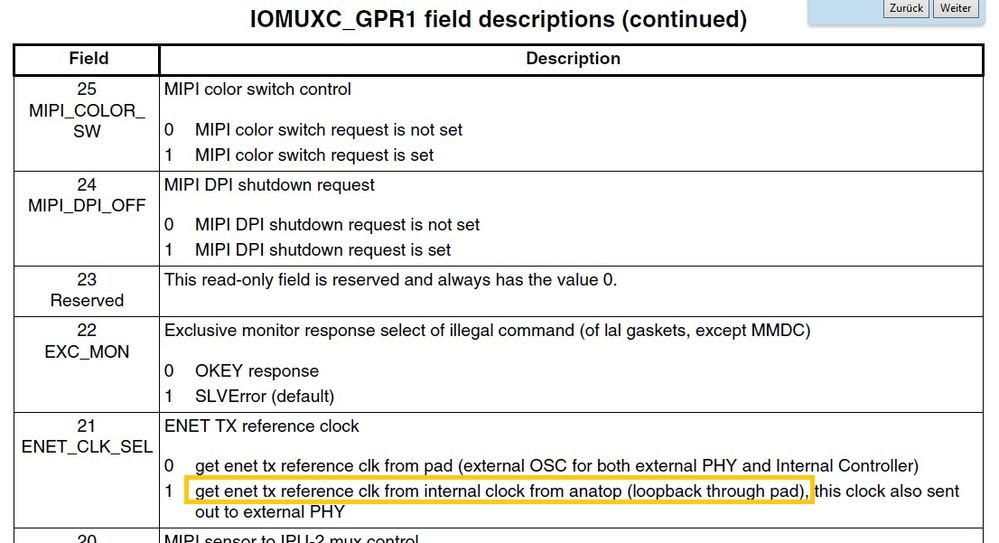

ENET_CLK_SEL - get enet tx reference clk from internal clock from anatop (loopback through pad), this clock also sent out to external PHY

IOMUXC_SW_MUX_CTL_PAD_GPIO16 - ENET_REF_CLK(signal)

It is possible to use ENET_REF_CLK(pad) then as GPIO ? (IOMUXC_SW_MUX_CTL_PAD_ENET_REF_CLK)

I found this diskussion:

-------------------------------------------------------------------------------------------

iMX6 RGMII + ENET_REF_CLK/ENET_TX_CLK

FrankLiu 21.05.2013 19:54

In RGMII Mode, only the pin "ENET_REF_CLK" could used as 125M reference clock input.

The 125M reference clock could be from PHY chip, or external oscillator, and could also be routed from GPIO_16(need software configuration). also?

In RMII Mode, only two pins "GPIO_16" and "RGMII_TX_CTL" could be used as the 50M reference clock. The clock source could be from external oscillator or internal PLL, need software configuration. Please refer the document "I.MX6 Hardware Development Guide", Chapter 11

--------------------------------------------------------------------------------------------

It is possible to use the internal PLL 125MHz for RGMII without external PHY or external oscillator ?

So the workaround GPIO_16

it's confusing to me

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mathias,

Not sure if I understand your question. The i.MX6 processor doesn't have an internal ENET PHY, it only has the controller. You have to place an external PHY connected to this controller so your system is RGMII capable. Now, about the clock, the processor needs a 125MHz one at the ENET_REF_CLK pin. This can come from an external oscillator or from the processor's GPIO16 pin, but this GPIO has to be connected to the ENET_REF_CLK pin externally, there's no way to take the signal from there inside the processor.

Please let me know if I misunderstood anything or if you need anything else.

Best regards.

Jorge.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mathias,

Not sure if I understand your question. The i.MX6 processor doesn't have an internal ENET PHY, it only has the controller. You have to place an external PHY connected to this controller so your system is RGMII capable. Now, about the clock, the processor needs a 125MHz one at the ENET_REF_CLK pin. This can come from an external oscillator or from the processor's GPIO16 pin, but this GPIO has to be connected to the ENET_REF_CLK pin externally, there's no way to take the signal from there inside the processor.

Please let me know if I misunderstood anything or if you need anything else.

Best regards.

Jorge.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have connected the GPIO16 pin externally to the ENET_REF_CLK pin in order to use as 125MHz reference clock.

According to Freescale technical support (via my distributor) this is not supported.

If you say It is as you wrote above, how do I need to setup the GPIO16 and ENET_REF_CLK registers in the CPU to achieve this?

Register Name="IOMUXC_SW_MUX_CTL_PAD_GPIO16" Address="0x020E0248" Value="0x????????"

Register Name="IOMUXC_SW_PAD_CTL_PAD_GPIO16" Address="0x020E0618" Value="0x????????"

Register Name="IOMUXC_ENET_REF_CLK_SELECT_INPUT" Address="0x020E083C" Value="0x????????"

Register Name="IOMUXC_SW_MUX_CTL_PAD_ENET_REF_CLK" Address="0x020E01D4" Value="0x????????""

Register Name="IOMUXC_SW_PAD_CTL_PAD_ENET_REF_CLK" Address="0x020E04E8" Value="0x????????""

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jorge,

you understand the question correctly.

> iMX6 Hardware Development Guide "12.4.1 Using the GPIO_16 pin to generate the reference clock"

Well, is it not possible to use a Daisy Chain register like RMII (50MHz) , to take the signal from there inside the processor ?

....it would be easier, not to route a 125MHz clock.

> iMX6Q Reference Manual

best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mathias,

Unfortunately there's no way to route the 125MHz clock internally like it is the case for the 50MHz one. The 125MHz clock has to be output at the GPIO16 and then routed back to the ENET_REF_CLK.

Best regards.

Jorge.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jorge,

in my setup i would like to remove PHY crystal so i'm hoping to generate 25 MHz from GPIO16, route it to the PHY and then route back the 125MHz clock from this to the ENET_REF_CLK.

does this setup work?

in any case it seems to me there is quite some confusion on the reference manual as there are two different ENET_REF_CLK signals to be dealt with. one is thesignal that can go to GPIO16(pin R2)/RGMII_TX_CTL (pin C23), which as far as i understand can be the output from the internal PLL and/or the input to the phy in RMII mode while the other one, called ENET_REF_CLK (pin V22) is the reference clock for the RGMII... maybe it would be good to differentiate these names given they're different things...