- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX6 ECSPI CS & timing issues

i.MX6 ECSPI CS & timing issues

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX6 ECSPI CS & timing issues

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear All,

I'm facing several issues with communication between an i.MX6Q ECSPI2 and an FPGA. Goal is to write 8bits address and read a 32bits value as fast as we can.

In my DTS file I set-up ECSPI2 to use SCLK/MISO/MOSI/SS0 and I wrote my own fpga kernel driver (kernel rel_imx_3.14.52_1.1.0_ga is compiled with imx-spi driver). You can find both at the end of this post.

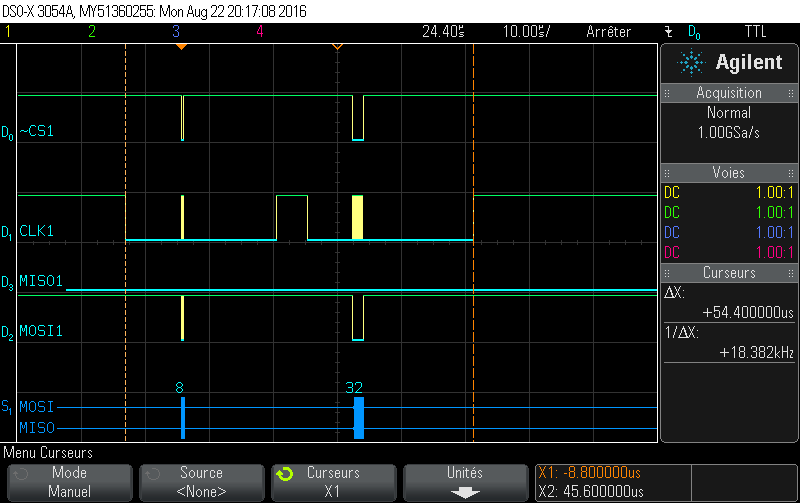

First, here is a capture of two SPI transfert in one SPI message :

Issue 1 : CS have to stay enabled between 8bits address writing and 32bits value reading.

Even if I set explicitely cs_change to 0 in my kernel driver, CS is disabled between the two bursts. I assume that I have to set SS_CTL to 0 but I have no idea how to do that in my driver

Note : If I change CS from SS0(DISP0_DAT18 - ALT2) to GPIO5_IO12 (DISP0_DAT18 - ALT5) this CS issue disappear - see oscilloscope print bellow - but I'd prefer to use native ECSPI CS.

Issue 2 : Why Is there a CLK tick between the two SPI message?

This issue is the same than the one describe here : https://community.nxp.com/message/625531#comment-625531 but solution have not been found yet.

Issue 3 : Time to take / release SPI communication is huge

As you can notice in the oscilloscope prints the time to take / release the SPI communication is really disappointing. I assume this is because SPI communication is handled by the kernel instead of the ECSPI bloc. Is there any way to change that?

Issue 4 : How to handle a 40bits SPI message with BURST ECSPI capability in my FPGA kernel driver?

-------------------------------------------------------------

=== DTS File ===

&ecspi2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2>;

fsl,spi-num-chipselects = <1>;

cs-gpios = <0>;

status = "okay";

fpga: fpga {

compatible = "eca,fpga";

reg = <0>;

spi-max-frequency = <20000000>;

};

};

&iomuxc {

ecspi2 {

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX6QDL_PAD_DISP0_DAT17__ECSPI2_MISO 0x100b1

MX6QDL_PAD_DISP0_DAT16__ECSPI2_MOSI 0x100b1

MX6QDL_PAD_DISP0_DAT19__ECSPI2_SCLK 0x100b1

MX6QDL_PAD_DISP0_DAT18__ECSPI2_SS0 0x100b1

>;

};

};

}

=== SPI driver ===

static int eca_fpga_reg_read(void *context, unsigned int reg, unsigned int *out)

{

struct device *dev = context;

struct spi_transfer t[2];

struct spi_message m;

u8 address;

__le32 val;

int ret;

mutex_lock(&spi_lock);

address = (reg << 1) | 0x1;

spi_message_init(&m);

memset(t, 0, sizeof(t));

t[0].tx_buf = &address;

t[0].len = sizeof(address);

t[0].cs_change = 0;

t[0].bits_per_word = 8;

t[1].rx_buf = &val;

t[1].len = sizeof(val);

t[1].bits_per_word = 32;

spi_message_add_tail(&t[0], &m);

spi_message_add_tail(&t[1], &m);

ret = spi_sync(to_spi_device(dev), &m);

mutex_unlock(&spi_lock);

if (ret)

return ret;

*out = cpu_to_le32(val);

return 0;

}

Any advice/hint/solution is more than welcome :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Julien

1. "cs_change" is not used in nxp ecspi driver (please check attached

Linux Manual Chapter 37) and sources/dts documentation :

In general one can add support for it using "of_get_named_gpio" in spi_imx_probe()

function. To avoid CS disabling between the two bursts it is necessary to set ECSPIx_CONREG

BURST_LENGTH with data burst and provide algorithm to avoid emptying TX FIFO, untill

all bits data sent out.

2. issue was not confirmed by nxp expert, in particular one can pay attention to

ERR009606 eCSPI: In master mode, burst lengths of 32n+1 will transmit incorrect data

3. timing may be affected by OS overheads, so one can try to optimize it removing

unused modules and tasks with heavy graphic.

4. set ECSPIx_CONREG[BURST_LENGTH] for 40 data burst and provide such algorithm

so TX FIFO was never empty, untill all data sent.

Note, NXP has service for helping customers with porting drivers:

http://www.nxp.com/support/nxp-professional-services:PROFESSIONAL-SERVICE

Pro-Support contact www.nxp.com/prosupport

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------