- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

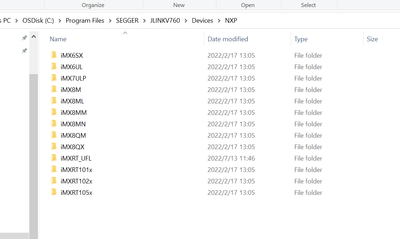

Working RT1062xxxxB HyperFLASH device in JLINKDevice.xml file

our MIMXRT1062CVJ5B hardware is configured with a S26KS512SDPBHI020 HyperFLASH memory.

When I configure my RT1062 in Boot Mode 0 and attach the iMX-MCUBootUtility application, it detects the RT1062 as well as the HyperFLASH. I am able to erase the FLASH and program it.

But when I attempt to connect via my J-Link controller, I am not able to detect or program the HyperFLASH. I am able to load code into RT1062 RAM and run/debug without any problem, but when I attempt to program the HyperFLASH I continue to get errors.

Does anyone see another edits to my JLinkDevices.xml that I have not made that will make this work?

Thanks

<Device>

<ChipInfo Vendor="NXP" Name="MIMXRT1062xxxxB" WorkRAMAddr="0x20000000" WorkRAMSize="0x00080000" Core="JLINK_CORE_CORTEX_M7" Aliases="MCIMXRT1062; MIMXRT1062xxx5B; MIMXRT1062CVL5B; MIMXRT1062xxx6B; MIMXRT1062DVL6B" />

<FlashBankInfo Name="HyperFlash" BaseAddr="0x60000000" MaxSize="0x04000000" Loader="Devices/NXP/iMXRT105x/NXP_iMXRT105x_HyperFlash.elf" LoaderType="FLASH_ALGO_TYPE_OPEN" />

</Device>

Is this the recommended solution from NXP? I would have expected a solution more integrated into or with MCUXpresso to support h/w that is also provided on the NXP provided development board (the RT1060 development board has HyperFLASH part)?

Hi @tbiberdorf ,

Yes, you are right!

The RT-UFL is designed by our NXP expert, and it also can works with JLINK+MCUXPresso, that's why I recommend you, it can support QSPI, hyperflash, octalflash, very easy to use.

This is the JLINK with MCUXPresso +RT-UFL.

https://www.cnblogs.com/henjay724/p/15430619.html

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

kerry

Hi @tbiberdorf ,

From your description, your MIMXRT1062CVJ5B hardware is configured with a S26KS512SDPBHI020 HyperFLASH memory is totally working, as the MCUBootUtility already can do the write and erase.

Now, just the JLINK debugger lack the flashdriver.

As the new JLINK driver didn't add the related hyperflash driver, just the default flashdriver is used for the QSPI flash:

So, you can't make it works.

Don't worry, we have another Jlink flashdriver named as RT-UFL, you can refer to it:

https://github.com/JayHeng/RT-UFL

To the JLINK driver install with RT-FUL, please refer to this post:

https://www.cnblogs.com/henjay724/p/14942574.html

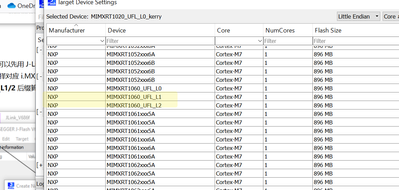

When you select the device, use the following _L1, or L2, that is for the hyperflash.

Wish it helps you!

Best Regards,

kerry

Hi Kerry

This provide solution does not make sense. I've been working on implementing it, but the numbers representing the FLASH size do not make any sense.

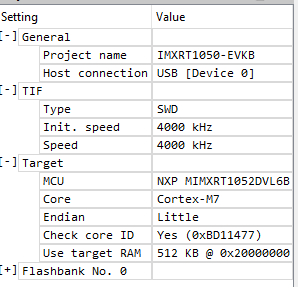

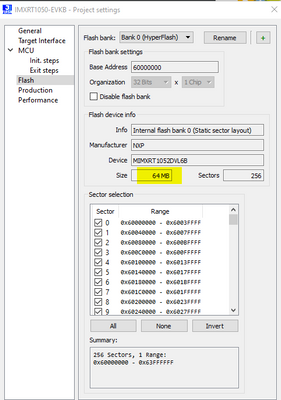

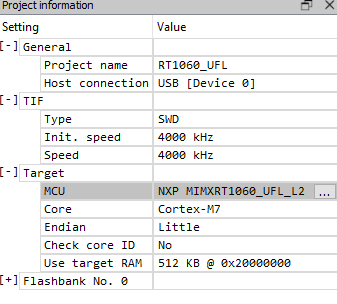

When I compare to my working connection to my IMXRT1050-EVKB I see that the assigned FLASH is 64MB, as expected:

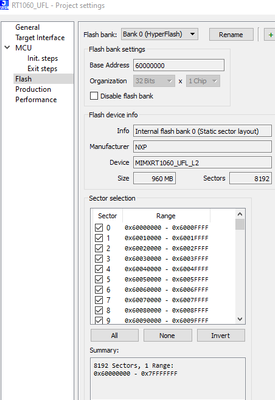

But the provided driver patch has the flash size at an extreme size of 960MB which is much larger than the expected 64MB.

This is what my .xml edit specifies:

<Device>

<ChipInfo Vendor="NXP"

Name="MIMXRT1060_UFL_L2"

WorkRAMAddr="0x20000000"

WorkRAMSize="0x00080000"

Core="JLINK_CORE_CORTEX_M7"

Aliases="MIMXRT1061xxx5A; MIMXRT1061xxx6A; MIMXRT1062xxx5A; MIMXRT1062xxx6A" />

<FlashBankInfo Name="HyperFlash"

BaseAddr="0x60000000"

MaxSize="0x04000000"

MaxSize="0x08000000"

Loader="Devices/NXP/iMXRT_UFL/MIMXRT_FLEXSPI_UFL_512B_64KB.FLM"

LoaderType="FLASH_ALGO_TYPE_OPEN" />

</Device>

Hi @tbiberdorf ,

This point is easy to realize, as the ongoing :MIMXRT_FLEXSPI_UFL_512B_64KB.FLM

is defined to the larger memory. ,_L1/2 used for Hyper Flash(Page size 512 Bytes,Sector size 4KB/64KB)

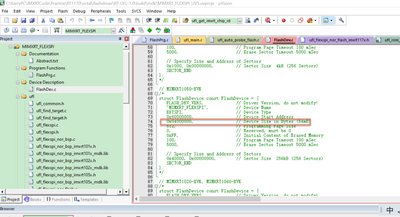

You can check the RT-UFL source code, in FlashDev.c, The above

MIMXRT_FLEXSPI_UFL_512B_64KB.FLM

is:

struct FlashDevice const FlashDevice = {

FLASH_DRV_VERS, // Driver Version, do not modify!

"MIMXRT_FLEXSPI", // Device Name

EXTSPI, // Device Type

0x00000000, // Device Start Address

0x40000000, // Device Size in Bytes (1GB)

FLASH_DRV_PAGE_SIZE, // Programming Page Size

0, // Reserved, must be 0

0xFF, // Initial Content of Erased Memory

3000, // Program Page Timeout 100 mSec

15000, // Erase Sector Timeout 15000 mSec

// Specify Size and Address of Sectors

FLASH_DRV_SECTOR_SIZE, 0x00000000, // Sector Size 4kB (256 Sectors)

SECTOR_END

};

That's why you find the size is large, as you know, our RT-UFL is not only used for the 64MB flash, but it also can support the large flash sizes.

So, if you care about the JLINK interface FLASH size, you totally can modify the RT-UFL source code, generate the new .flm, then test it again.

I think, now, you don't need to care about size at first, after your board RT1060+hyperflash can program and boot works OK, then we can modify the source code, that is easy to realize.

Best Regards,

Kerry

Hello Kerry

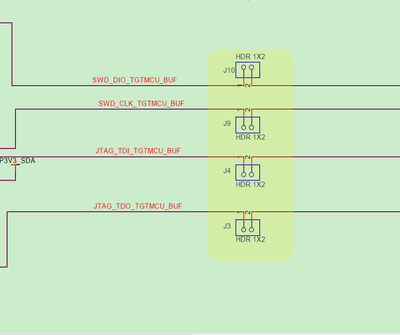

Sorry, but none of these suggestions you provided have made any difference in my communication with my HyperFLASH. I have been able to purchase a MIMXRT1060-EVKB development board and had the needed modifications to support HyperFLASH operations (as per the attached schematics comments page 12)

I've made the suggested modification to my Jlink Devices file as you suggested:

<!-- -->

<!-- NXP (iMXRT106x IoT / HyperFlash) -->

<!-- -->

<Device>

<ChipInfo Vendor="NXP"

Name="MIMXRT1060_UFL_L2"

WorkRAMAddr="0x20200000"

WorkRAMSize="0x00080000"

Core="JLINK_CORE_CORTEX_M7"

Aliases="MIMXRT1061xxx5A; MIMXRT1061xxx6A; MIMXRT1062xxx5A; MIMXRT1062xxx6A" />

<FlashBankInfo Name="HyperFlash"

BaseAddr="0x60000000"

MaxSize="0x04000000"

MaxSize="0x08000000"

Loader="Devices/NXP/iMXRT_UFL/MIMXRT_FLEXSPI_UFL_512B_64KB.FLM"

LoaderType="FLASH_ALGO_TYPE_OPEN" />

</Device>

and I am still unable to make any useful communication with my development board.

When I programmed my FLASH with the NXP-MCUBootUtility.exe, then viewed my FLASH memory with MCUXpresso IDE, I can see the MCUXpresso GUI FLASH tool provides details that it was successful in the erase of my FLASH part, but yet still shows that it has been programmed, see attached image MCUXpresso IDE view FLASH.png

I had modify the FLASH driver to many different options and none seem to provide any success in even erasing my FLASH memory.

Can anyone provide any useful suggestions that can show that the RT1062 works with HyperFLASH memory???

Thanks

Hi @tbiberdorf ,

Please follow me do some testing at first:

1. Check the hardware connection is good

I checked your picture: MemoryMods.jpg

That is correct in the hardware modification points, but we still need to check it is really working.

2. Please run this code in the internal RAM:

SDK_2_12_0_MIMXRT1060-EVKB\boards\evkbmimxrt1060\driver_examples\flexspi\hyper_flash\polling_transfer

Check the printf information, whether the erase, program and read are all passed?

If yes, it means the hardware totally works

3. Seems you also use the NXP-MCUBootUtility.exe,

Do you use the serial download mode to download app, then check the boot, whether that works or not?

serial download mode: SW4 1-OFF,2-ON, 3-OFF, 4-ON

Internal boot mode: SW4 1-OFF, 2-ON, 3-ON, 4-OFF

3. When use the JLINK, please remove these jumper: J3,J4,J9,J10

4. JLINK plus+hyperflash+RT-UFL

Do you try the JFLASH in the JLINK driver, what's the detail test result, after you do the connection, program app, what's the error reported with the original RT-UFL, device: MIMXRT1060_UFL_L1

Don't use your modified firmware, just the original firmware, what's the result?

I write a RT1170 document with RT-UFL, maybe you also can refer to it, the test method is useful to you.

https://community.nxp.com/t5/i-MX-RT-Knowledge-Base/RT1170-Octal-flash-enablement/ta-p/1498369

Please share me your JFlash or the JLINK command related situation, I will help you to check it.

In the previous time, I have tested MIMXRT1060-EVK+hyperflash, that works OK with RT-UFL, the EVKB should be the same.

5. Please note, when you use the hyperflash, your SDK app FCB need to be modified:

const flexspi_nor_config_t hyperflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

3

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_ExternalInputFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.columnAddressWidth = 3u,

// Enable DDR mode, Wordaddassable, Safe configuration, Differential clock

.controllerMiscOption =

(1u << kFlexSpiMiscOffset_DdrModeEnable) | (1u << kFlexSpiMiscOffset_WordAddressableEnable) |

(1u << kFlexSpiMiscOffset_SafeConfigFreqEnable) | (1u << kFlexSpiMiscOffset_DiffClkEnable),

.sflashPadType = kSerialFlash_8Pads,

.serialClkFreq = kFlexSpiSerialClk_133MHz,

.sflashA1Size = 64u * 1024u * 1024u,

.dataValidTime = {16u, 16u},

.lookupTable =

{

// Read LUTs

FLEXSPI_LUT_SEQ(CMD_DDR, FLEXSPI_8PAD, 0xA0, RADDR_DDR, FLEXSPI_8PAD, 0x18),

FLEXSPI_LUT_SEQ(CADDR_DDR, FLEXSPI_8PAD, 0x10, DUMMY_DDR, FLEXSPI_8PAD, 0x06),

FLEXSPI_LUT_SEQ(READ_DDR, FLEXSPI_8PAD, 0x04, STOP, FLEXSPI_1PAD, 0x0),

},

},

.pageSize = 512u,

.sectorSize = 256u * 1024u,

.blockSize = 256u * 1024u,

.isUniformBlockSize = true,

};Or you can use the RT1050 SDK FCB directly.

Best Regards,

kerry

Hi Kerry

I've continued to attempt to get the suggested UFL code suggestions to work but it continues to fail.

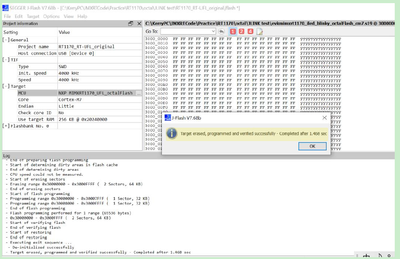

Now I do have the installed version of J-Flash version 7.68c working when I modified the JLinkDevices.xml file, please see attached zip of these two files.

I modified the flexspi_nore_config.c file to use hyperflash and made the needed changes in the project settings to support XIP operation.

I can use J-FLASH to program my target system, but I did notice that I need to first erase the FLASH before the program/verify operation will work, but after programmed and verified, I can then take the MXUXpresso debug configuration to "attach to running" settings and my IDE will attach to the modified code and allow me to view memory and step through code.

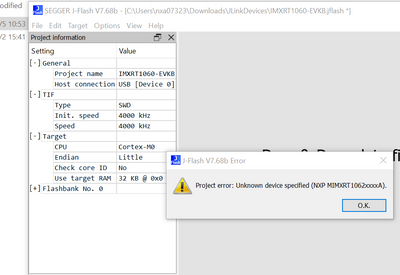

Why does MCUXpresso not support direct writing as it seems that I can perform these operations independent with j-FLASH. Also when I attempt to perform all these operations with the IMXRT1050-EVKB everything works smoothly???

I continue to see many references to RT1050 drivers and such in the RT106x interfaces, so I continue to wonder if anyone has ever got the IMXRT1060-EVKB to every work with HyperFLASH.

Thanks for any suggestions.

Hi @tbiberdorf ,

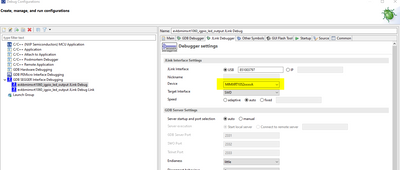

So, now, which device name you are using in both the JFLASH and the MCUXPresso JLINK debug configuration?

Normally, JFlash works, then the MCUXpresso IDE works, as the MCUXPresso IDE will call the related jlink driver, but you need to select the correct device name and the JLINK driver path.

I checked your attachment:

Do you still use the RT1050? I mean, you select the device name as:MIMXRT1050_UFL_L2?

I open your JFLASH project, didn't find your device name:

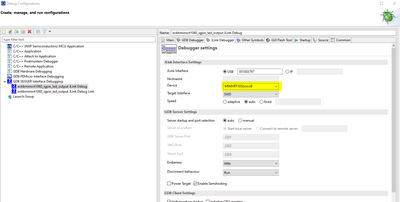

In the MCUXpresso IDE, debug configuration area, the JLINK device name should be the same as your JFLASH.

https://www.cnblogs.com/henjay724/p/15430619.html

The following picture also need to select the working JLINK driver file:

I have tested the MIMXRT1060-EVK+hyperflash, that works OK, as you know, EVKB is totally the same flash chip to the EVK.

Best Regards,

Kerry

When discussing this issue with the Future FAE, we found the solution using the provided Segger J-Flash release 7.68c

After doing the 5 modifications MCUXpresso is now able to write new SDK example code to HyperFLASH:

- Make all hardware adjustments to the development board (IMXRT1060-EVKB) to convert from QSPI to HyperFLASH.

- Create example SDK project (ie evkbmimxrt1060_igpio_led_output).

- Replace qspiflash config with a hyperflash config, inside the following xip source file .../xip/evkbmimxrt1060_flexspi_nor_config.c

#if 1

const flexspi_nor_config_t hyperflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_ExternalInputFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.columnAddressWidth = 3u,

// Enable DDR mode, Wordaddassable, Safe configuration, Differential clock

.controllerMiscOption =

(1u << kFlexSpiMiscOffset_DdrModeEnable) | (1u << kFlexSpiMiscOffset_WordAddressableEnable) |

(1u << kFlexSpiMiscOffset_SafeConfigFreqEnable) | (1u << kFlexSpiMiscOffset_DiffClkEnable),

.sflashPadType = kSerialFlash_8Pads,

.serialClkFreq = kFlexSpiSerialClk_133MHz,

.sflashA1Size = 64u * 1024u * 1024u,

.dataValidTime = {16u, 16u},

.lookupTable =

{

// Read LUTs

FLEXSPI_LUT_SEQ(CMD_DDR, FLEXSPI_8PAD, 0xA0, RADDR_DDR, FLEXSPI_8PAD, 0x18),

FLEXSPI_LUT_SEQ(CADDR_DDR, FLEXSPI_8PAD, 0x10, DUMMY_DDR, FLEXSPI_8PAD, 0x06),

FLEXSPI_LUT_SEQ(READ_DDR, FLEXSPI_8PAD, 0x04, STOP, FLEXSPI_1PAD, 0x0),

},

},

.pageSize = 512u,

.sectorSize = 256u * 1024u,

.blockSize = 256u * 1024u,

.isUniformBlockSize = true,

};

#else

const flexspi_nor_config_t qspiflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_LoopbackFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.sflashPadType = kSerialFlash_4Pads,

.serialClkFreq = kFlexSpiSerialClk_100MHz,

.sflashA1Size = 8u * 1024u * 1024u,

.lookupTable =

{

// Read LUTs

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xEB, RADDR_SDR, FLEXSPI_4PAD, 0x18),

FLEXSPI_LUT_SEQ(DUMMY_SDR, FLEXSPI_4PAD, 0x06, READ_SDR, FLEXSPI_4PAD, 0x04),

},

},

.pageSize = 256u,

.sectorSize = 4u * 1024u,

.blockSize = 64u * 1024u,

.isUniformBlockSize = false,

};

#endif - Modify the Debug Configurations and replace the MIMXRT1062xx6A to MIMXRT1052xxxA

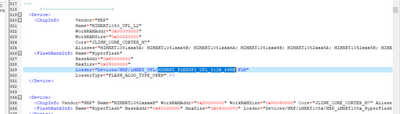

- Added the following Device to the Segger JLinkDevices.xml file:

</Device>

<Device>

<ChipInfo Vendor="NXP" Name="MIMXRT1062xxx6A" WorkRAMAddr="0x20000000" WorkRAMSize="0x00080000" Core="JLINK_CORE_CORTEX_M7" JLinkScriptFile="Devices/NXP/iMXRT105x/NXP_iMXRT105x.pex" />

<FlashBankInfo Name="HyperFlash" BaseAddr="0x60000000" MaxSize="0x04000000" Loader="Devices/NXP/iMXRT105x/NXP_iMXRT105x_HyperFlash.elf" LoaderType="FLASH_ALGO_TYPE_OPEN" />

</Device>

Thanks for your information, so at last, still use the RT1050 hyperflash flashdriver, that's works with RT1060, as the RT1060 flexSPI can compatible with the RT1050 flexSPI.

So, just use that for downloading now.

To your mentioned RT-UFL debug the situation, we will also test it in our side.

Best Regards,

Kerry