- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- SGTL5000 and Non-Standard Sample Rates

SGTL5000 and Non-Standard Sample Rates

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SGTL5000 and Non-Standard Sample Rates

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear all,

I'm in the process of developing a minimalist USB audio interface around the SGTL5000 and competition's LPC1347 (clocked at 72 MHz), and I am having a hard time figuring out the best clock configuration. Since MCLK is going to be obtained by integer frequency division, it is likely going to have to be 12 MHz. From what I can tell, this leaves me with three options:

- Using the PLL and having the SGTL as I2S master (inconvenient for several reasons),

- an "odd" sample rate of 46.875 kHz (12000000 Hz / 256, which would be by far my preferred choice), or

- a just as hacky solution with 44.1 kHz LRCLK, 1.5 MHz SCLK, and transmission breaks in between samples.

In order to figure this out, I would appreciate knowing more about how the SGTL internally synchronizes to I2S data - can I, for instance, use a higher SCLK and just wait with the transmission of the next sample until the end of the LRCLK interval? Are there any known cases where such situation has been successfully resolved with the SGTL as I2S slave? What would be the corresponding settings?

Thanks,

Matthias

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Matthias

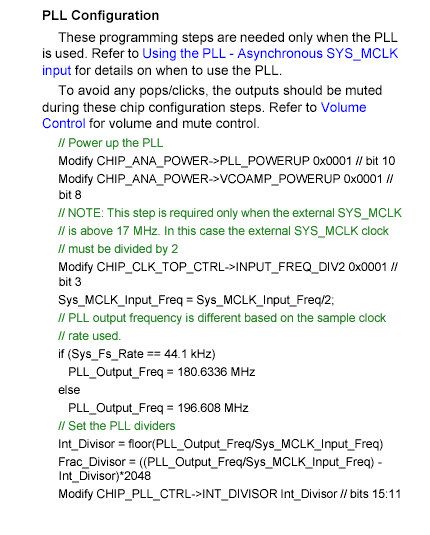

one can use SGTL5000 internal PLL for obtaining necessary frequencies.

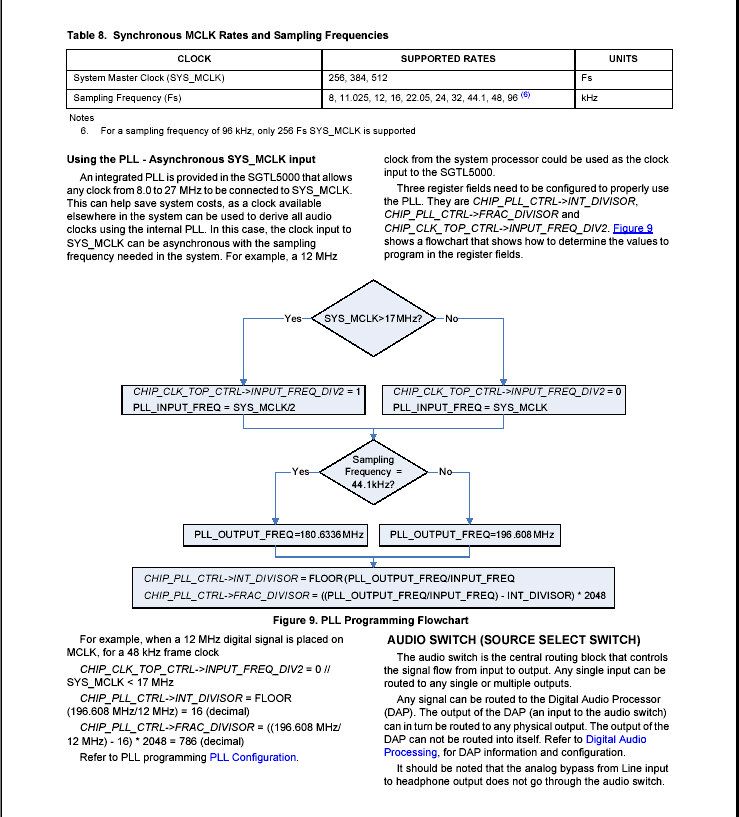

This is described in SGTL5000 p.14

sect.2.2.2 PLL Configuration AN3663 AN3663, SGTL5000 Initialization and Programming

Regarding usage "higher SCLK", I am afraid SGTL5000 does not support such kind of algorithm.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

And ... we have audio out! (It also helps to probe the line outs, not the line ins :smileyhappy:)

Thanks Igor for your smooth response.

Matthias

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your reply. From the manual, I take it that using the PLL requires that the SGTL become master on the I2S bus, correct?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes correct, as described in SGTL5000 p.18 :

The I2S_LRCLK and I2S_SCLK can be programmed as

master (driven to an external target) or slave (driven from an

external source). When the clocks are in slave mode, they

must be synchronous to SYS_MCLK. For this reason the

SGTL5000 can only operate in synchronous mode (see

Clocking) while in I2S slave mode.

In master mode, the clocks are synchronous to

SYS_MCLK or the output of the PLL when the part is running

in asynchronous mode.

~igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you. Just implemented that, and by accident also found out that the sample rate can in fact be set to "odd" values, at least as long as they're in the interval of 44.1 to 48 kHz. To achieve f_target (in kHz), the PLL output freq (also in kHz can be calculated as pll_output_freq = 196608 / 48 * f_target. For f_target = 44.1 kHz, this results in pll_output_freq=180633.6 kHz. So the divider for 48 kHz is 16.384 -- accidentally rounding it to 16.000 results exactly in a sample rate of 46.875 kHz :-)