- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Reset of SNVS_LP on some boards but not others

Reset of SNVS_LP on some boards but not others

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Reset of SNVS_LP on some boards but not others

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

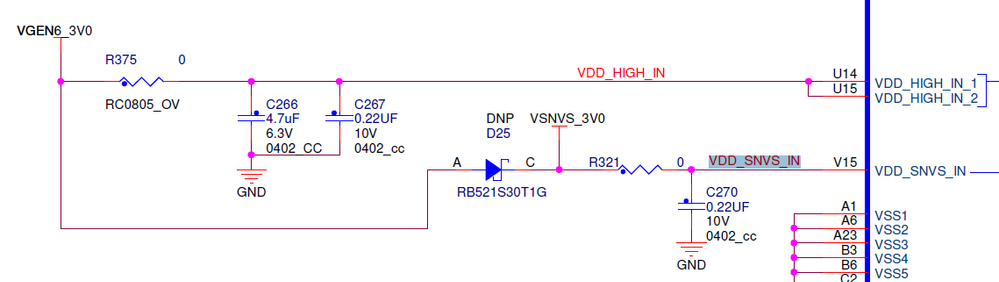

In our IMX6SX based boards, we are currently experience an occasional (on some boards but not others) loss of content of SNVS_LP registers when we are doing a WDOG reset (with POR). It does not seem to be related to the VDD_VSNVS_IN power source: there are no voltage drops there.

1. Is anyone aware of the possible sources of lp_por signal? It's not very well documented in the Reference Manuals.

2. Does anyone know if the BOOTROM is handling any violations in its default config ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Weidong,

We have been measuring the voltage of VSNVS_3V0 during the resets that cause the loss of SNVS_LP data and using 2 different Test Points and an Oscilloscope with 1 ms step and there were no voltage drops. It was stable at ~2.96 V.

That is why, having relatively high confidence in the stability of VSNVS_3V0 that we measured during the problematic resets, and in the software boot loader which we are debugging early in it's execution, I started looking at the SNVS System Security Monitor. If you have some other avenue that we can look at, please let us know.

Some other things of note:

- this only happens if the wdog reset we are using, also issues the WDOG_B signal.

- we are not having this problem when we are running on battery, without AC connection.

- on the problematic boards, this only starts happening a couple of minutes after the initial COLD POWER ON. This means that the first couple of resets will not manifest the SNVS_LP register reset, while any subsequent reset will always manifest it.

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexandru,

>>we are not having this problem when we are running on battery, without AC connection.

(1)The battery you mentioned is the working battery of the board, not the li coin cell battery of snvs, right?

(2)If yes, the batter is used to supply PIMC, right?

>>on the problematic boards, this only starts happening a couple of minutes after the initial COLD POWER ON. This means that the first couple of resets will not manifest the SNVS_LP register reset, while any subsequent reset will always manifest it.

If VSNVS_3V0 is stable, no any drops during COLD RESET, SNVS_LP shouldn't be changed.

In addition, would you like to attach your schematic here?

Have a nice day!

BR,

weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexandru,

See my advice below, please!

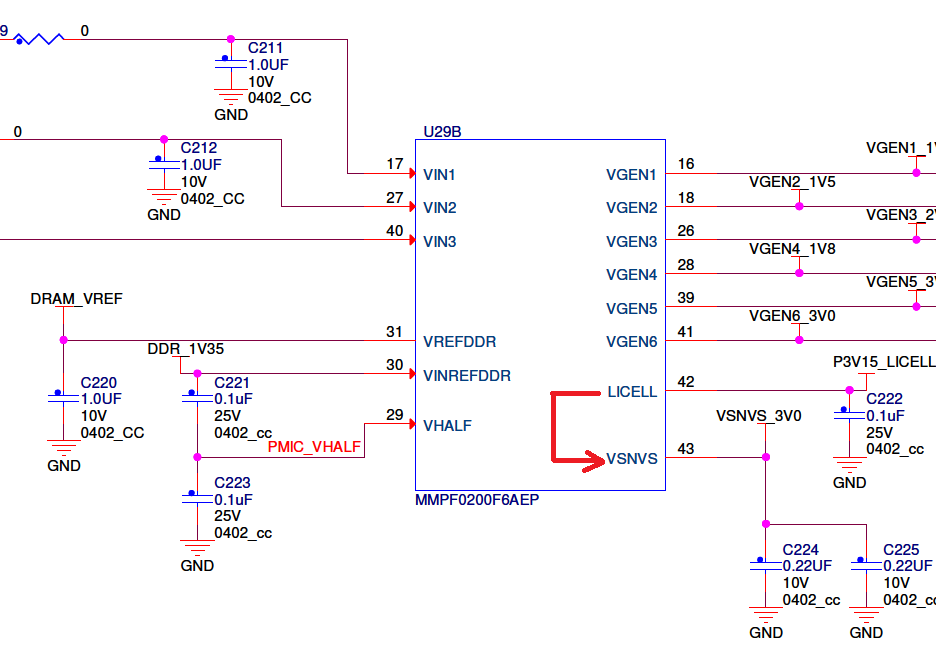

1. In order to keep the contents of snvs register or RTC unchanged, it is necessary to ensure that vsnvs_3v0 power supply is stable.

See schematic below, please!

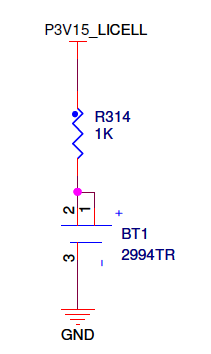

2. If your reset is operating PWRON pin of PMIC, it means cold reset occurs, which is equivalent to powering the board off and then back on,so at the moment of power off, P3V15_LICELL must supply power to VDD snvs in. This is to ensure that the contents of snvs register are not lost.

3. for your questions

You have some boards that are normal and some boards that are abnormal. Therefore, it is recommended that you first check whether the power of Li coin cell is normal, without doubting the snvs module inside the CPU.

Hope above advice is helpful for you!

Have a nice day!

BR,

Weidong