- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- RT1024 Double bank with memory offset

RT1024 Double bank with memory offset

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

RT1024 Double bank with memory offset

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In our system, we have RT1024 and RT1064 processors.

For each microprocessor, we implemented a dual-bank bootloader mechanism to handle updates.

Since our code is quite large, we cannot execute it from RAM and instead execute it from flash.

Our images are compiled with static addresses corresponding to bank one.

When image two boots, we want to perform an address translation.

There is a simple solution for the RT1064 that involves using the IOMUXC_GPR_GPR30, 31, and 32 registers.

The operating principle is explained in the following documentation:

https://www.nxp.com/docs/en/application-note/AN12240.pdf

However, we haven't found an equivalent mechanism for the RT1024.

Does one exist?

If not, do you have a solution to suggest?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I found a post similar to my needs:

However, I can't get it to work. Here are the steps I took:

I started a project from scratch with only a flashing debug LED. Modified the linker:

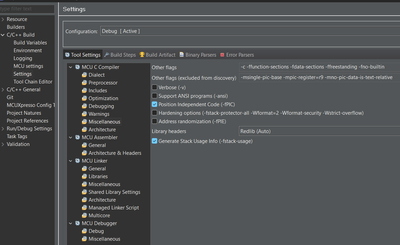

Setting the compilation options:

Adding the correct reference in the r9 register:

I load the .bin file at address 0x60080000 I created a bootloader project with only a jump to address 0x6008238D, which is the address of the reset handler 0x6000238D + the offset.

During the jump, the code fails.

I must be missing an operation, can you help me?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

One thing that seems strange to me is the contents of the .map in the .got section.

I don't know if it's normal for there to be so little.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I think I'm close to the goal.

I've hard-coded all the values into the startup file.

When I disassemble the code, something seems strange: the function addresses are static despite the -pFIC option.