- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Problems with CS1 control fail when using EIM interface in u-boot

Problems with CS1 control fail when using EIM interface in u-boot

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Problems with CS1 control fail when using EIM interface in u-boot

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear community,

We occured the following problems during testing on the reference SABRESD board(MCIMX6Q-SDB).

Problems with CS1 control fail when using EIM interface in u-boot

** Questions **

- Is the below setting correct?

- In kernel, success to write data to EIM CS0 / CS1 using ioremap function.

In uboot environment, how to write data to an address without ioremap function?

The environment and settings are shown below.

1. uboot version : v2013.10-r0

2. Kernel version : L3.0.35-r37.14

3. modify u-boot source code

- file : board/freescale/mx6sabresd

- function : board_late_init()

- PAD Setting

iomux_v3_cfg_t weim_pads[] = {

MX6_PAD_EIM_OE__WEIM_WEIM_OE | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_RW__WEIM_WEIM_RW | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_CS0__WEIM_WEIM_CS_0 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_CS1__WEIM_WEIM_CS_1 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_LBA__WEIM_WEIM_LBA | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_BCLK__WEIM_WEIM_BCLK | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_EB1__WEIM_WEIM_EB_1 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA15__WEIM_WEIM_DA_A_15 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA14__WEIM_WEIM_DA_A_14 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA13__WEIM_WEIM_DA_A_13 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA12__WEIM_WEIM_DA_A_12 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA11__WEIM_WEIM_DA_A_11 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA10__WEIM_WEIM_DA_A_10 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA9__WEIM_WEIM_DA_A_9 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA8__WEIM_WEIM_DA_A_8 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA7__WEIM_WEIM_DA_A_7 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA6__WEIM_WEIM_DA_A_6 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA5__WEIM_WEIM_DA_A_5 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA4__WEIM_WEIM_DA_A_4 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA3__WEIM_WEIM_DA_A_3 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA2__WEIM_WEIM_DA_A_2 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA1__WEIM_WEIM_DA_A_1 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_DA0__WEIM_WEIM_DA_A_0 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT12__WEIM_WEIM_D_8 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT13__WEIM_WEIM_D_9 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT14__WEIM_WEIM_D_10 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT15__WEIM_WEIM_D_11 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT16__WEIM_WEIM_D_12 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT17__WEIM_WEIM_D_13 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT18__WEIM_WEIM_D_14 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_CSI0_DAT19__WEIM_WEIM_D_15 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A16__WEIM_WEIM_A_16 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A17__WEIM_WEIM_A_17 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A18__WEIM_WEIM_A_18 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A19__WEIM_WEIM_A_19 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A20__WEIM_WEIM_A_20 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A21__WEIM_WEIM_A_21 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A22__WEIM_WEIM_A_22 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A23__WEIM_WEIM_A_23 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A24__WEIM_WEIM_A_24 | MUX_PAD_CTRL(EIM_PAD_CTRL),

MX6_PAD_EIM_A25__WEIM_WEIM_A_25 | MUX_PAD_CTRL(EIM_PAD_CTRL)

};

imx_iomux_v3_setup_multiple_pads(weim_pads,ARRAY_SIZE(weim_pads));

- IOMUXC_GPR1 / CS1GCR1 / CS1GCR2 / CS1RCR1 / CS1RCR2 / CS1WCR1 / CS1WCR2 / CS1WCR Setting

void __iomem *eim_reg = MX6_IO_ADDRESS(WEIM_BASE_ADDR +0x18);

//GPR1 register/////////////////////////////////////////////////////////////////////

reg = readl(IOMUXC_BASE_ADDR + 0x4); // GPR1 register CS0/CS1 enable

reg &= ~0x07ffffff;

reg |= 0x1b;

writel(reg, IOMUXC_BASE_ADDR + 0x4);

//CS1GCR1///////////////////////////////////////////////////////////////////////////

writel(0x00051081,eim_reg); //CS1GC[18:16](DSZ -> 101 : 8bit port resides on DATA[15:8]

//CS1GCR2///////////////////////////////////////////////////////////////////////////

writel(0x00000000,(eim_reg+ 0x4)); //CS1GCR2

//CS1RCR1///////////////////////////////////////////////////////////////////////////

writel(0x16000202,(eim_reg+ 0x8)); //CS1RCR1

//CS1RCR2///////////////////////////////////////////////////////////////////////////

writel(0x00000002,(eim_reg+ 0xC)); //CS1RCR2

//CS1WCR1///////////////////////////////////////////////////////////////////////////

writel(0x16002082,(eim_reg+ 0x10)); //CS1WCR1

//CS1WCR2///////////////////////////////////////////////////////////////////////////

writel(0x00000000,(eim_reg+ 0x14)); //CS1WCR2

//CS1WCR////////////////////////////////////////////////////////////////////////////

writel(0x00000000,(eim_reg+ 0x90)); //CS1WCR

- Data Write

*(unsigned char *)(0x8400000) = 0x0A; // CS0

*(unsigned char *)(0xC400000) = 0x0A; // CS1

4. How to check the operation

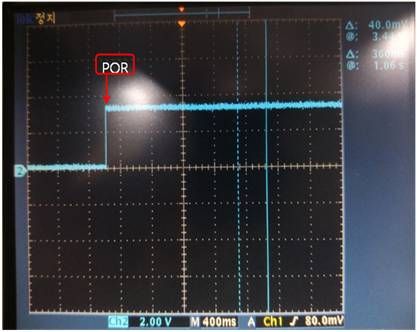

- Check EIM CS1(R627) operation using oscilloscope

5. Test result

- EIM CS1 pin does not move

- When writing data (*(unsigned char *)(0x8400000) = 0x0A;) ,

uboot init no longer proceeds and kernel is not loaded.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear igor,

Thank you for quickly response.

In the kernel, both CS0 and CS1 are successfully written.

So in uboot, We set the same value as in Kernel for the following registers.

IOMUXC_GPR1 / CS1GCR1 / CS1GCR2 / CS1RCR1 / CS1RCR2 / CS1WCR1 / CS1WCR2 / CS1WCR

We want to access EIM CS1 using the ioremap function as in the kernel.

We understand that to use the ioremap function, we must enable the MMU.Is right?

Please let us know, How can We enable the MMU in uboot?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Igor,

Thank you for your answer.

We have worked again with the eim paralle nor example in mx6qsabreauto.c file.

We use CS0 (64MB), CS1 (64MB) and write data to CS0 and CS1 respectively as shown below.

CS0 write succeeds, but a fault occurs when writing to CS1.

* (unsigned char *) (0x8400000) = 0x0A; // CS0 Write -> Success

udelay (100);

* (unsigned char *) (0xC400000) = 0x0A; // CS1 Write -> Fail

In Kernel, write is successful in both CS0 and CS1 using ioremap function.

Is there anything else I need to do to write using CS1 in uboot?

If enable MMU in uboot, can ioremap be used?

if so, Is there a way to enable the MMU in uboot?

Thank you for your help.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi HAE

in uboot one can printf eim cs0, cs1 settings and compare them.

Also one can check iomux cs1 settings.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi HAE

parallel nor is used with eim on sabre ai board and one can look at its uboot:

uboot/board/freescale/mx6qsabreauto/mx6qsabreauto.c

uboot-imx.git - Freescale i.MX u-boot Tree

In particular one can check if eim clock is enabled in CCM_CCGR6

As SABRESD board (MCIMX6Q-SDB) uses EIM signals for other

purposes, one needs to check uboot code and remove EIM signals from

usage by other modules.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------